60 Millionen Euro teurer Komplex soll 2026 betriebsbereit sein

Chemnitz, 5. Oktober 2023. Um seine Forschungen an neuen Materialien, Prozessen, Zuverlässigkeitstests und Systemen für die Mikroelektronik zu verstärken, will das Fraunhofer-Institut für Elektronische Nanosysteme (Enas) in Chemnitz für 60 bis 70 Millionen Euro ein neues Reinraum-Technikum bauen und das hauseigene Zuverlässigkeits-Labor ausbauen. Das hat Enas-Chef Prof. Harald Kuhn angekündigt. Der neue Testchipfabrik soll 2026/27 betriebsbereit sein.

Alter Reinraum entstand in Honecker-Ära

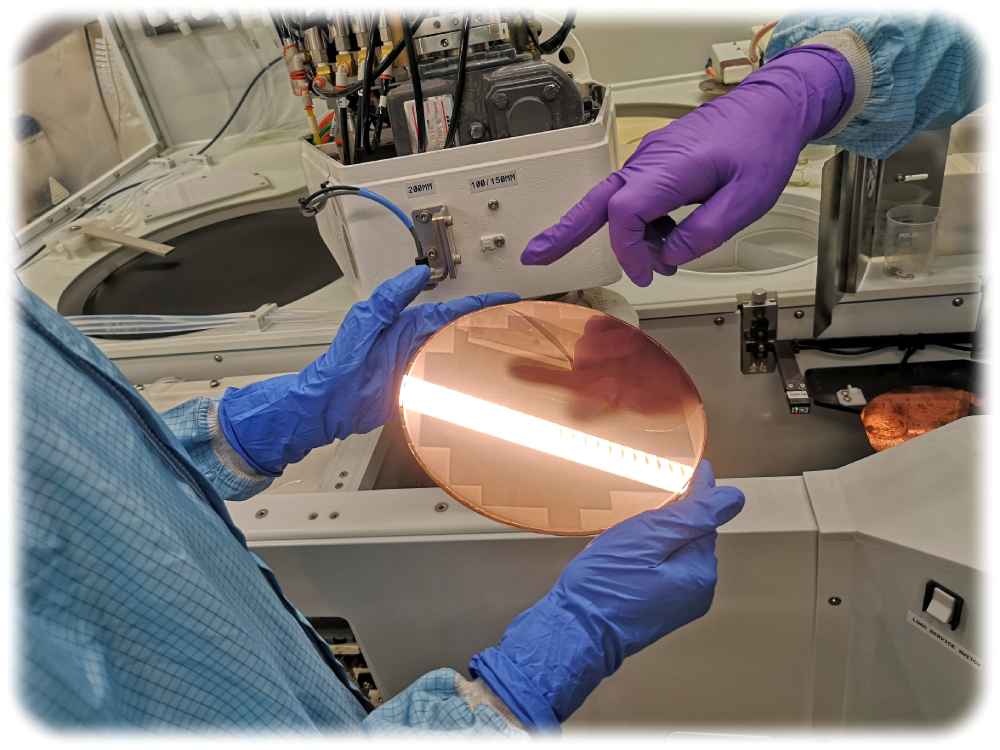

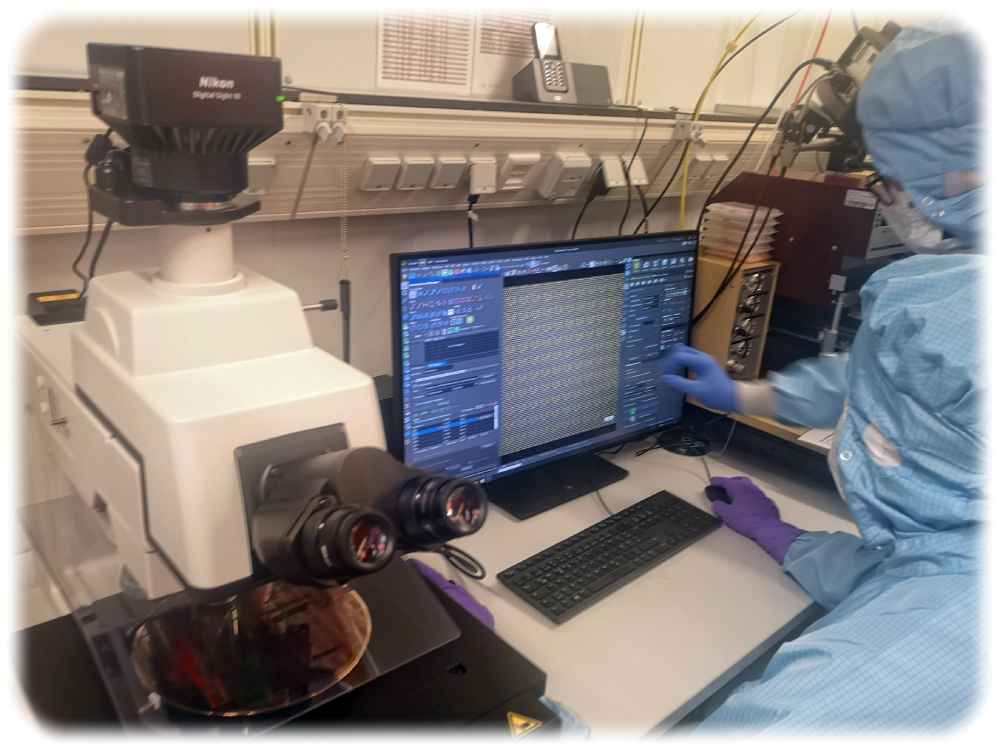

Seit seiner Gründung im Jahr 2008 nutzt das Enas einen Reinraum, dessen Grundstruktur auf das Jahr 1979 zurückgeht. Dort haben die Fraunhofer-Ingenieure bisher Chip-Fertigungsanlagen und Testtechnik im Wert von rund 100 Millionen Euro installiert. Eine Modernisierung pressiert nun zunehmend, weil die sächsische Mikroelektronik wieder auf Wachstumskurs ist und die Technologiebreite zunimmt: TSMC siedelt sich an, Infineon baut eine neue Megafab, Globalfoundries und Bosch wollen ebenfalls expandieren – und Technologien wie Leistungshalbleiter einer neuen Generation, Quanten-Datenverarbeitung oder Beschleunigerchips für „Künstliche Intelligenz“ spielen eine wachsende Rolle. Zudem ist auch das Enas zuletzt stark gewachsen: Hatte das Institut im Jahr 2010 erst 91 Beschäftigte, sind es inzwischen 250. „Wir sind in den letzten Jahren stark gewachsen“, berichtete der Instituts-Chef. Aus all diesen Gründen möchte Kuhn einen moderneren Reinraum, in dem er neben bereits vorhandener Technik auch neueren Anlagen zum Beispiel für die Atomlagenabscheidung (ALD) installieren lassen will.

Erst kürzlich hatte bereits das Dresdner Fraunhofer-Photonikinstitut IPMS neue Ausbaupläne für sein „Center for Advanced CMOS & Heterointegration Saxony“ bekanntgegeben.

Vom Mikrosystem bis zum Quantencomputer

Im Reigen der sächsischen Mikroelektronik-Forschungsinstitute hat sich das Enas vor allem auf Miniatursysteme aus Schaltkreisen, Sensoren und Aktoren, moderne Verpackungstechnologien für Chips sowie Wafer und Mikrosysteme aus verschiedenen Materialien fokussiert.

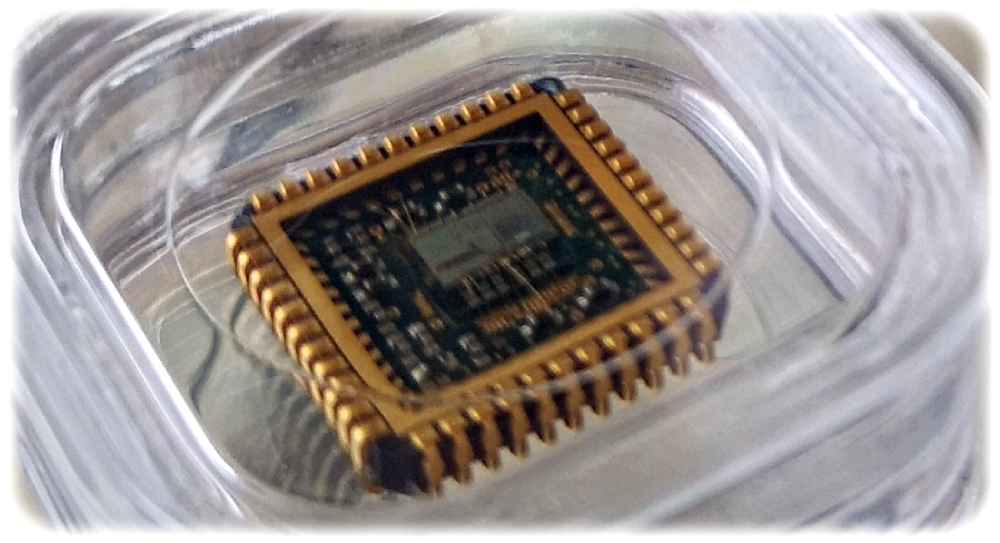

Asic-Schaltkreis mit Gyroskop vom Fraunhofer-Enas. Solche Mikro-Kreiselkompasse brauchen beispielsweise Smartphones, um ihre Lage und Bewegung zu bestimmen. Foto: Heiko Weckbrodt

Auf der neuen Forschungsagenda steht beispielsweise die Integration von ganz unterschiedlichen Halbleiterstrukturen nach dem Lego-Zusammensteck-Prinzip – die sogenannte „Heterointegration“. Zudem wollen Kuhn und sein Team bessere Ionenfallen für Quantencomputer-Chips sowie neuronenähnliche Memristor-Chips entwickeln und verstärkt Künstliche Intelligenzen für die Prozessanalyse in Chipfabriken fit machen.

Chemnitzer entwickeln neue Testtechnik für Leistungselektronik

Auch arbeitet das Enas-Laborteam an besseren Zuverlässigkeits-Tests für neue Schaltkreise. Mit neuer Messtechnik aus dem Enas sollen Unternehmen wie Infineon oder Bosch künftig leichter Leistungselektronik mit Blick darauf analysieren können, welche Stromstärke und Spannungen sie aushält, bevor sie durchschmort. Das ist wichtig für künftige Generationen von Solar- und Windkraftanlagen, Elektroautos und Bahntechnik. Dabei will sich das Enas insbesondere neue „Highpower“-Tests für Bipolartransistoren mit isolierter Tor-Elektrode (IGBTs) entwickeln, aber auch elektrische Zuverlässigkeitstests für Leistungselektronik aus den Hoffnungsträgern Galliumnitrid und Siliziumkarbid. „Wir werden die Testmöglichkeiten für diese Elektronik revolutionieren“, versprach Enas-Chef Kuhn dem sächsischen Wissenschaftsminister Sebastian Gemkow (CDU) und verwies auf die hohen weltweiten Wachstumsraten für Leistungselektronik dieser Klasse.

Halbleiterforschung in Chemnitz seit den 1970ern

Zum Hintergrund: Der zentrale Wachstumskern für die sächsische Mikroelektronik war und ist zwar Dresden. Doch auch in Chemnitz hat die Forschung an Halbleitern und Mikrostrukturen eine lange Tradition: 1979 entstand in Karl-Marx-Stadt ein „Technikum Mikroelektronik“ als gemeinsame Einrichtung der Technischen Hochschule und der Industrie. Daraus wurde 1991 das „Zentrum für Mikrotechnologien“ (ZfM), das heute zur Uni Chemnitz gehört, aber in Personalunion von Enas-Chef Prof. Kuhn geleitet wird. Das ZfM verfügt derzeit über zwei Reinräume mit insgesamt 1000 Quadratmetern Fläche. Die Anlagen dort sind allerdings nur für Siliziumscheiben (Wafer) mit Durchmessern bis zu 200 Millimeter ausgelegt. Große Chipfabriken und auch ein Teil der Dresdner Fraunhofer-Institute verwenden hingegen 300-mm-Anlagen.

Autor: Heiko Weckbrodt

Quellen: Auskünfte Kuhn, Enas, Oiger-Archiv, TUC/IDW

Zum Weiterlesen:

Paneuropäische Mikroelektronik-Forschungsplattform – auch CNT und Enas dabei

Chemnitzer Kreiselkompass kennt auch im Stahllabyrinth den Weg

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!

Du muss angemeldet sein, um einen Kommentar zu veröffentlichen.