Im ehemaligen Plastic-Logic-Reinraum nahe der Fabs von Bosch, Jenoptik und künftig auch TSMC im Dresdner Norden installiert Fraunhofer bereits eine Mikroelektronik-Forschungsfabrik: das Zentrum für fortgeschrittene CMOS-Technologien und Heterointegration Sachsen. Hier soll auch ein Teil der „paneuropäischen Plattform“ entstehen. Foto: Heiko Weckbrodt

Mit Imec und Leti soll für 850 Millionen Euro paneuropäische virtuelle Forschungs-Chipfabrik entstehen

Dresden, 14. September 2023. Nach TSMC und Infineon plant nun auch Fraunhofer neue Investitionen in den Mikroelektronik-Standort Sachsen: Gemeinsam mit den Halbleiter-Großforschungszentren Imec in Belgien und Cea-Leti in Frankreich sowie weiteren Partnern will das Fraunhofer-Institut für Photonische Mikrosysteme (IPMS) aus Dresden für 850 Millionen Euro eine „Paneuropäische Plattform“ für die Forschungsproduktion neue Schaltkreise und Chiptechnologien aufbauen – einen Teil davon in Dresden und Chemnitz. Voraussetzung ist, dass EU, nationale und regionale Regierungen dafür Chipgesetz-Fördergeld genehmigen beziehungsweise bereitstellen. Das hat IPMS-Chef Prof. Harald Schenk bei einem Besuch des sächsischen Wissenschaftsministers Sebastian Gemkow (CDU) im neuen „Zentrum für fortgeschrittene CMOS-Technologien und Heterointegration Sachsen“ (Cachs) in Dresden angekündigt.

Konzept der „Forschungsfabrik Mikroelektronik Deutschland“ bald in europäischen Maßstab?

Geplant ist demnach, die besten Forschungsreinräume in Europa zu einer Art virtueller Chip-Fabrik zusammenzuschließen, die zusammen alle Prozessschritte in der langen Mikroelektronik-Wertschöpfungskette abdeckt und auch neue Technologien entwickeln kann. Damit könnte Europa seine mangelnde Schlagkraft bei umfangreichen Entwicklungsvorhaben im Vergleich zu den großen Mikroelektronik-Konzernen in Amerika und Asien womöglich teilweise wettmachen. Ein ähnliches Konzept liegt bereits der „Forschungsfabrik Mikroelektronik Deutschland“ (FMD) zugrunde, die 2017 von der Fraunhofer-Gesellschaft und der Leibniz-Gemeinschaft initiiert wurde. Teil der paneuropäischen Initiative sei es nun, diese Forschungs- und Pilotkapazitäten in Deutschland, Frankreich, Belgien und weiteren Ländern besser zu vernetzen und so zu ertüchtigen, dass sie den neuesten technologischen Stand mitbestimmen, erklärte Schenk.

80 bis 100 Millionen Euro sollen im Falle eines Zuschlags nach Sachsen fließen

Das Geld dafür wollen die Partner im Zuge des „Europäischen Chipgesetzes“ beantragen. Das läuft letztlich darauf hinaus, dass im Wesentlichen die jeweiligen nationalen und regionalen Regierungen diese Investitionen bezahlen sollen. Konkret für den Freistaat ist vorgesehen, neue Mikroelektronik-Anlagen für rund 80 bis 100 Millionen Euro anzuschaffen. Die sächsischen Forscher wollen diese Maschinen im Cachs, im IPMS, im Centrum für Nanoelektroniktechnologie (CNT) und im „All Silicon System Integration Dresden“ (Assid) in Dresden sowie im Fraunhofer-Institut für Elektronische Nanosysteme (Enas) in Chemnitz installieren, womöglich auch im Fraunhofer-Institutsteil für Entwicklung Adaptiver Systeme (EAS) in Dresden.

Chiplet-Technologie im Dresdner Fokus

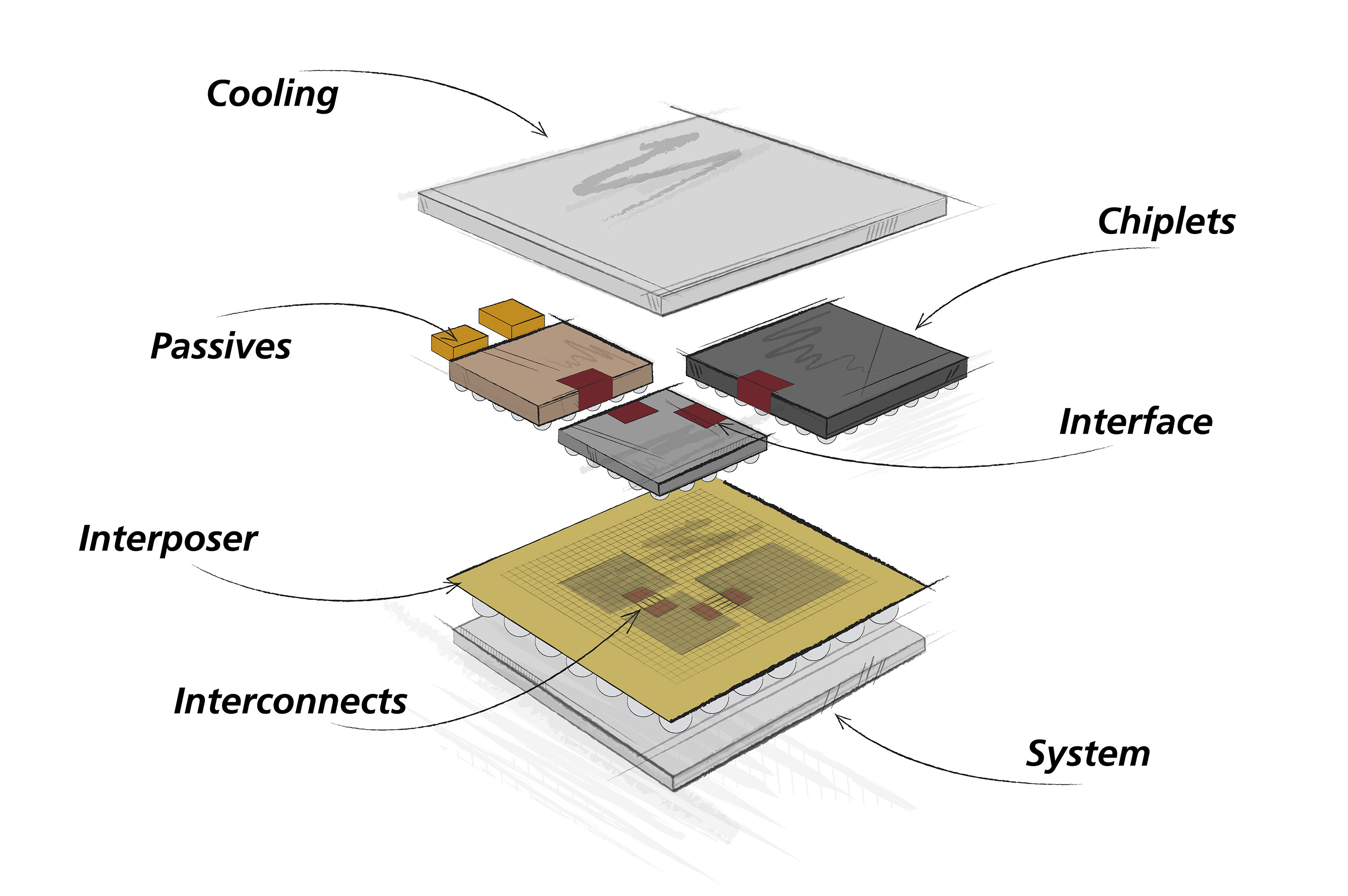

Schenk will im Zuge der paneuropäischen Plattform insbesondere die Fähigkeit der europäischen Mikroelektronik stärken, eigene „Chiplets“ zu entwickeln und herzustellen. Diese „Chiplets“ kombinieren Prozessorkerne, Speicher, Sensoren und andere Spezialschaltkreise und -elemente zu einem System, das wie ein einziger Chip wirkt. Diese Teilchips können sogar in ganz unterschiedlichen Fabriken hergestellt werden, müssen schließlich aber in den Reinraumfabrik zu einem Ganzen hochpräzise auf Chip- oder Wafer-Ebene zusammengesetzt werden. Unterm Strich können damit mehr mikroelektronische Funktionen auf kleinstem Raum untergebracht werden. Zudem steigt die Ausbeute und sinkt der Stromverbrauch im Vergleich zum Versuch, all diese Funktionen auf einem Chip „aus einem Guss“ unterzubringen.

Die Grafik zeigt den dreidimensionalen Aufbau, die Kontakte (Interconnects) und Schnittstellen (Interfaces) zwischen Chiplets und verschiedenen Chipebenen. Grafik: Fraunhofer-IIS / EAS

Bisher beherrschen erst wenige Akteure diese noch junge und anspruchsvolle Technologie für die Massenproduktion. Dazu gehört übrigens auch der taiwanesische Branchenprimus TSMC, der sich demnächst in Dresden ansiedelt. Hier will und muss Europa dringend nachziehen, um mit seiner – ohnehin bereits spezialisierten – Mikroelektronik wettbewerbsfähig zu bleiben.

TSV-Anlagen auf der Wunschliste

Auf der Wunschliste von Fraunhofer in Dresden und Sachsen stehen nun beispielsweise Anlagen, mit denen sich über- und nebeneinandergestapelte Teilchips elektrisch durchkontaktieren lassen, zum Beispiel durch direkte Kontaktiertunnel durchs Silizium (englisch: „through silicon via“, kurz: TSV).

„Quasimonolithische Integration“: Chips wie Aufkleber übereinanderschichten

Mit diesen und weiteren Anschaffungen im Rahmen der paneuropäischen Initiative möchten Prof. Schenk und seine Kollegen auch neuere Ansätze für die dreidimensionale Integration verschiedener Chiparten – die sogenannte 3D-Heterointegration – erproben. Dazu gehört unter anderem die „Quasimonolithische Integration“ (QMI). Dabei erzeugen die Mikroelektroniker beispielsweise erst getrennt Speicherchips, Sensoren und Prozessorkerne, schleifen sie dann ganz dünn, fügen sie wie ein 3D-Puzzle in dünnen Stückchen übereinander und ziehen dann jeweils eine Begradigungsschicht ein, so dass die Siliziumscheibe danach wie ein ganz normaler Wafer weiterprozessiert werden kann. Diese und ähnliche Technologien könnten gerade für den Automobilbau, Maschinenhersteller, „Industrie 4.0“-Anbieter und andere Mikroelektronik-Kunden in Europa besonders interessant sein.

Autor: Heiko Weckbrodt

Quellen: Auskünfte Schenk/IPMS, Vor-Ort-Besuch, Oiger-Archiv

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!

Du muss angemeldet sein, um einen Kommentar zu veröffentlichen.