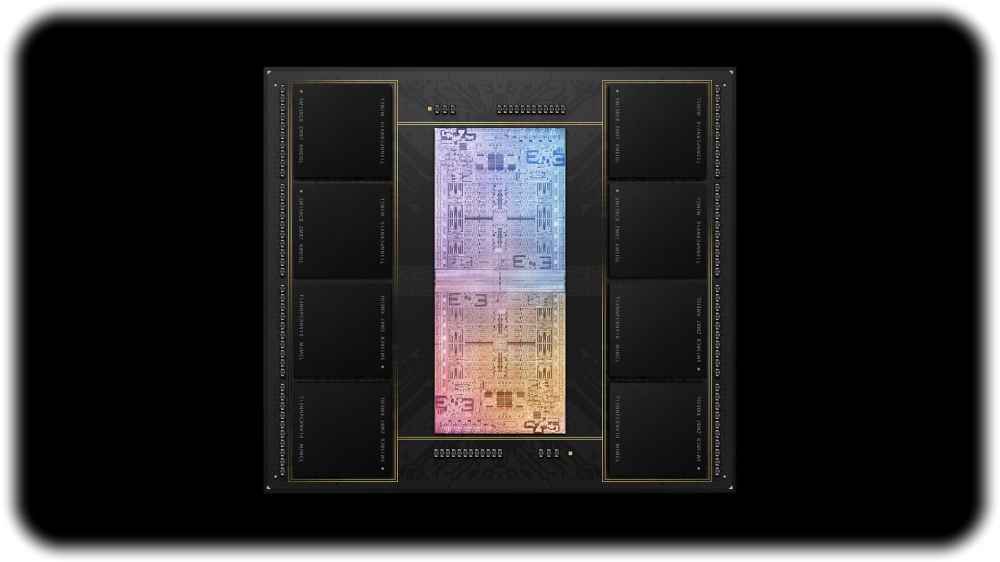

Für den Doppelprozessor M1 Ultra setzt Apple auf Chiplet-Technologien, bei denen zwei Chips durch sogenannte „Silizium-Interposer“ fusioniert werden. Die Produktion übernimmt TSMC in einem 2,5D-Verfahren. Foto: Apple

30 Prozent jährliches Marktwachstum für neue Chip-Verpackungstechniken prognostiziert

Dresden, 29. Juni 2023. Die 3D-Integration von Schaltkreisen wird in den kommenden Jahren eine wichtige Rolle beim Vorstoß hin zu mehr Leistungsdichte in der Mikroelektronik spielen. Das haben Experten aus der Halbleiterindustrie unisono auf der internationalen Konferenz „Smarter Systems Through Heterogeneous Integration“ des Branchenverbandes „Semi Europe“ in Dresden eingeschätzt.

Prognose: 3D-Architekturen liefern Schlüssel zu besserer „Künstlicher Intelligenz“

„3D-Architekturen werden die Grenzen des Machbaren insbesondere für Künstliche Intelligenz hinausschieben“, prognostizierte Halbleiter-Direktorin Emilie Jolivet vom französischen Marktforschungs-Unternehmen „Yole“. Um den Leistungsbedarf solcher und anderer rechenintensiver Schlüsseltechnologien zu bedienen, sei ein ganzheitliches dreidimensionales Chipdesign nötig.

Transistordichte zwar noch nicht am Ende – doch der Aufwand steigt enorm

Das Problem dahinter bewegt die Branche schon seit Jahren: Zwar war in der Anfangszeit der Mikroelektronik das sogenannte Mooresche Gesetz noch recht mühelos einzuhalten, laut dem sich die Transistor-Dichte in Schaltkreisen etwa alle anderthalb Jahre verdoppelt. Doch mittlerweile ist dieser Pfad hin zu mehr Rechenleistung extrem aufwendig und teuer geworden, was auch zu einer gewissen Marktbereinigung geführt hat: Nur noch wenige Großkonzerne wie TSMC oder Samsung – und mit Abstrichen auch Intel – beherrscht Strukturbreiten unterhalb von zehn Nanometern in der Massenproduktion. Neben die technologischen Aspekte im Fertigungsprozess treten thermische, energetische und finanzielle Probleme: Die Kosten für die nötigen Anlagen steigen zunehmend ins Astronomische. Auch stellen Abwärme und Energieverbrauch der klassisch geschrumpften Chipstrukturen die Hersteller vor enorme Herausforderungen.

AMD hat schon recht früh auf Chiplet-Konzepte gesetzt und seine Hauptprozessoren (CPUs) mit Grafikprozessoren (GPUs) kombiniert – hier ein Ryzen-Chip, der darauf beruht. Foto: AMD

Apple, AMD und auch die Chinesen setzen auf 3D- und Chiplet-Pfad

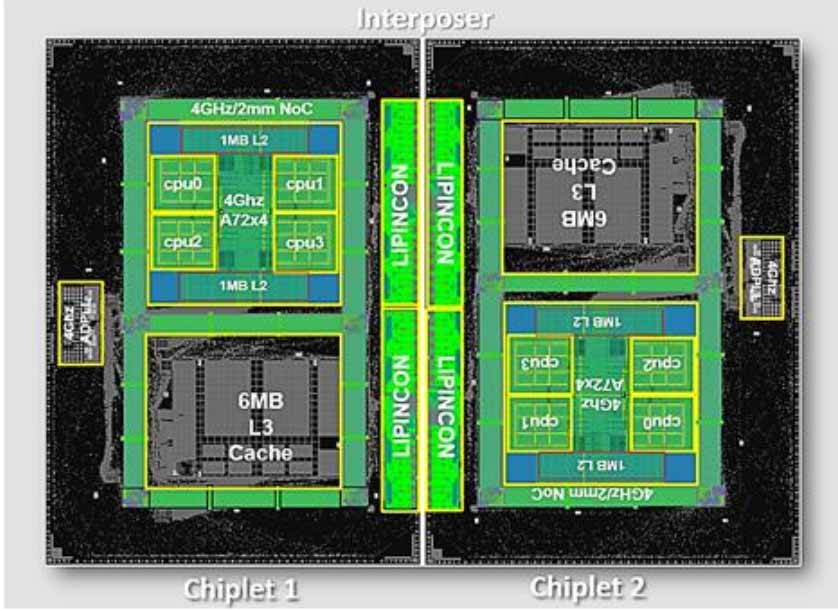

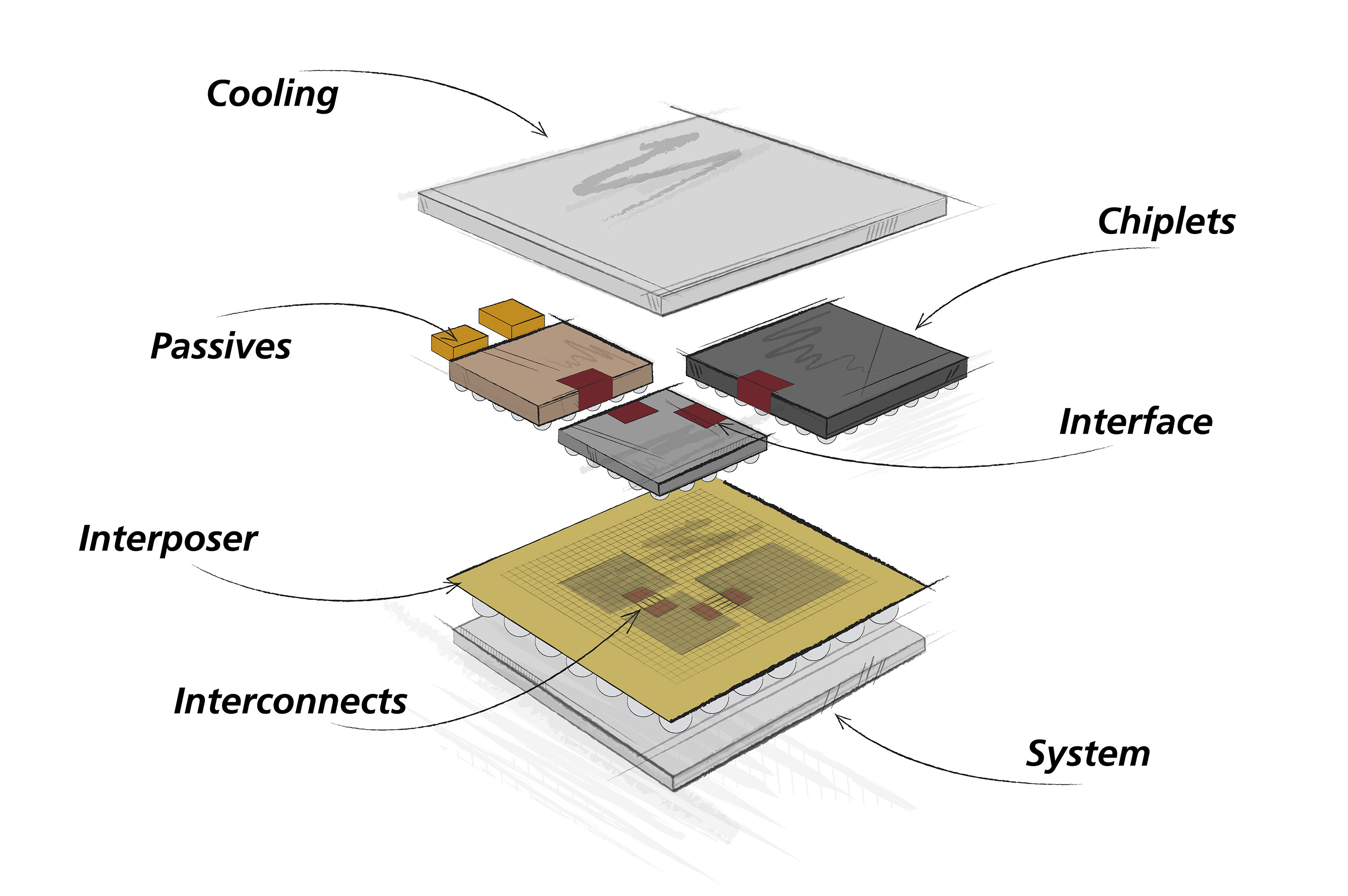

All dies hat den Fokus der Industrie ein Stück weit von den Kernprozessen der Chipfertigung („Frontend“) hin zu neuen Verpackungs-, Kontaktier- und Endmontagetechnologien („Backend“ beziehungsweise „Packaging“) für Schaltkreise gelenkt, hin zu Konzepten wie „Chiplets“, 3D- und 2,5D-Integration. Dabei werden beispielsweise unterschiedliche Schaltkreise, Sensoren, analoge Elemente und andere Funktionsblöcke dicht neben- oder übereinander zusammenfügt, durchkontaktiert und dann wie ein Computerchip in einem Gehäuse verpackt. Das können beispielsweise ein oder mehrere Zentralrechnerkerne (CPUs), Grafikprozessoren (GPUs), aber auch Speicher und Kommunikations-Bausteine sein. Bereits realisierte Beispiele dafür sind der „Ryzen“ von AMD, der „Meteor Lake“ von Intel, der bei TSMC produzierte „M1 Ultra“ von Apple oder der chinesische Kryptoschürfer-Chip „Jasminer X4“. Für vertikale Verbindungen setzt sich dabei immer mehr das „Hybrid Bonding“ durch, bei dem die noch unverpackten Schaltkreise („Dies“) über eingebettete Kupfer-Ballen („Pads“) verknüpft werden.

Mehr Ausbeute, weniger Kosten, mehr Leistungsdichte

Teils steht beim Einsatz solcher Techniken die Kostenfrage im Mittelpunkt. Denn die 2,5D- beziehungsweise 3D-integrierten Funktionsblöcke für ein Chiplet müssen nicht alle im selben, teuren Spitzenprozess gefertigt werden. Einige lassen sich durchaus in preiswerteren, weniger hochintegrierten Fertigungslinien produzieren. Zudem steigt bei kleineren Dies auch die Ausbeute im Vergleich zu monolithischen Großschaltkreisen. Meist steht auch – wie etwa bei Apple – das Motiv dahinter, mehr Rechenkraft oder – wie bei AMD – mehr Funktionalitäten auf kleinstem Raum zu packen.

Auch der weltweit größte Auftragsarbeiter TSMC in Taiwan arbeitet mit Chiplets – hier ein Prozessor für Supercomputer. Foto: TSMC

Yole: Markt für progressive Chip-Verpackung steigt auf knapp 80 Milliarden $

Und die Nachfrage für solch progressive Technologien wächst weltweit: Yole-Analystin Jolivet geht davon aus, dass der Markt für fortgeschrittenes Packaging von 44,3 Milliarden Dollar im Jahr 2022 bis zum Jahr 2028 auf 78,6 Milliarden Dollar steigt – bei jährlichen durchschnittlichen Wachstumsraten um die zehn Prozent. Im Teilmarkt für 2,5D- und 3D-Packaging sei indes sogar mit jährlichen Zuwachsraten um die 30 Prozent zu rechnen. Gerade das Spitzensegment wird allerdings bisher von nur wenigen Akteuren beherrscht. Dazu gehören insbesondere TSMC, Samsung, Intel, Hynix und die hierzulande wenig bekannte chinesische Gruppe „YMTC“. Bei etwas einfacher gestrickten Übergangstechnologien (2,5D) sind auch Amkor, UMC und weitere Unternehmen mit im Geschäft.

Die Grafik zeigt den dreidimensionalen Aufbau, die Kontakte (Interconnects) und Schnittstellen (Interfaces) zwischen Chiplets und verschiedenen Chipebenen. Grafik: Fraunhofer-IIS / EAS

Europa wiederum forscht zwar auch an 3D-, 2,5D- und Chiplet-Technologien, beispielsweise im belgischen Imec oder in den Fraunhofer-Einrichtungen Assid und EAS in Dresden. Doch eine eigene Massenproduktion im 3D-Packaging-Segment gibt es in Europa nicht. Diese Lücke versucht übrigens auch der „European Chips Act“ ein Stück weit zu schließen.

Autor: Heiko Weckbrodt

Quellen: Yole, Semi-3D-Gipfel Dresden, Oiger-Archiv

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!

Du muss angemeldet sein, um einen Kommentar zu veröffentlichen.