Fraunhofer Dresden gar mit dem „EMSA5-FS“ einen eigenen RISC-V-Prozessor entwickelt. Visualisierung: Fraunhofer IPMS

Fraunhofer-Institut IPMS stellt mit dem „EMSA5“ eigenen RISC-V-Prozessor vor – andere arbeiten an Neuro- und Quantenprozessoren

Dresden, 31. August 2023. Um Europa weniger abhängig von den Chipriesen in den USA und in Fernost zu machen, steigen Dresdner Mikroelektronik-Institute nach rund längerer Pause wieder ins Prozessor-Design ein. Dabei stehen neben Experimenten mit Neuro- und Quantenprozessoren vor allem die RISC-V-Architektur im Fokus. Auf dieses frei nutzbare und quelloffene „Reduced Instruction Set Computer V“ stützen sich vor allem die Ingenieure am freien Barkhausen-Institut und am Fraunhofer-Photonikinstitut (IPMS) in Dresden. Letztere haben mit dem „EMSA5“ nun einen eigenen RISC-V-Prozessor vorgestellt.

„Eine Revolution ausgelöst“

„Die Zugänglichkeit von RISC-V hat eine Revolution ausgelöst“, argumentieren die Fraunhofer-Experten. Denn damit gebe es „gegenüber kommerziellen – meist außereuropäischen – Lösungen eine unabhängige und offene Alternative“. Zudem sei mit RISC-V eine günstige Balance zwischen Energieverbrauch und Leistung möglich. Und dies ist eben besonders für Automobilelektronik in Elektrofahrzeugen wichtig, deren Akkus nicht zu stark durch die Bordcomputer belastet werden sollen. Richtig genutzt, könne diese Alternative zu Intel & Co. die technologische Souveränität Europas stärken, meinen die Dresdner Mikroelektroniker.

Europa will eigenes RISC-V-Ökosystem zimmern

Konkret beteiligen sich die RISC-V-Entwickler am IPMS an mehreren Verbundprojekten: Im Forschungsvorhaben „Tristan“ hilft Fraunhofer Dresden dabei, ein komplettes Ökosystem für den Entwurf und die Produktion industrienaher RISC-V-Chipsysteme aufzubauen. Und im Verbundprojekt „Imab-Edge“ arbeitet das IPMS an einem neuartigen Überwachungssystem für Brücken, Staudämme und andere Infrastruktur-Bauwerke mit. Die sollen künftig stärker als bisher mit Sensoren gespickt werden. Deren Daten sollen dann lokale „Künstliche Intelligenzen“ (Edge-KIs) überwachen, die auf RISC-V-Rechnern nach Dresdner Entwürfen laufen. Der dafür eingesetzte „EMSA5“ von Fraunhofer ein 32-Prozessor, der sich sowohl zu leistungsfähigen KI-Computer koppeln lassen soll, anderseits aber auch als „Einzelkämpfer“ den Stromverbrauch in mobilen eingebetteten Systemen dämpfen kann.

Prozessor-Entwurf spielte schon zu DDR-Zeiten eine Rolle in Dresden

Prozessordesign hat in Dresden durchaus Traditionen: Zu DDR-Zeiten waren zwar vor allem die Erfurter Chipfabriken für die Prozessor-Massenproduktion zuständig. Doch einige Entwicklungsarbeiten dafür – auch beim ostdeutschen 32-Bit-Prozessor-Nachbau – fanden im ZMD und bei Robotron Dresden statt. Nach der Wende fuhr zudem AMD in Dresden die Massenproduktion seiner „Athlons“ und anderer Prozessoren hoch – und baute hier schließlich auch Entwicklungskapazitäten für prozessornahe Betriebssysteme auf. Als sich AMD aus Sachsen zurück zog, schlossen die Amerikaner zwar auch dieses OSRC genannte Zentrum. Dennoch blieb viel Prozessor- und Betriebssystem-Expertise in der Stadt erhalten.

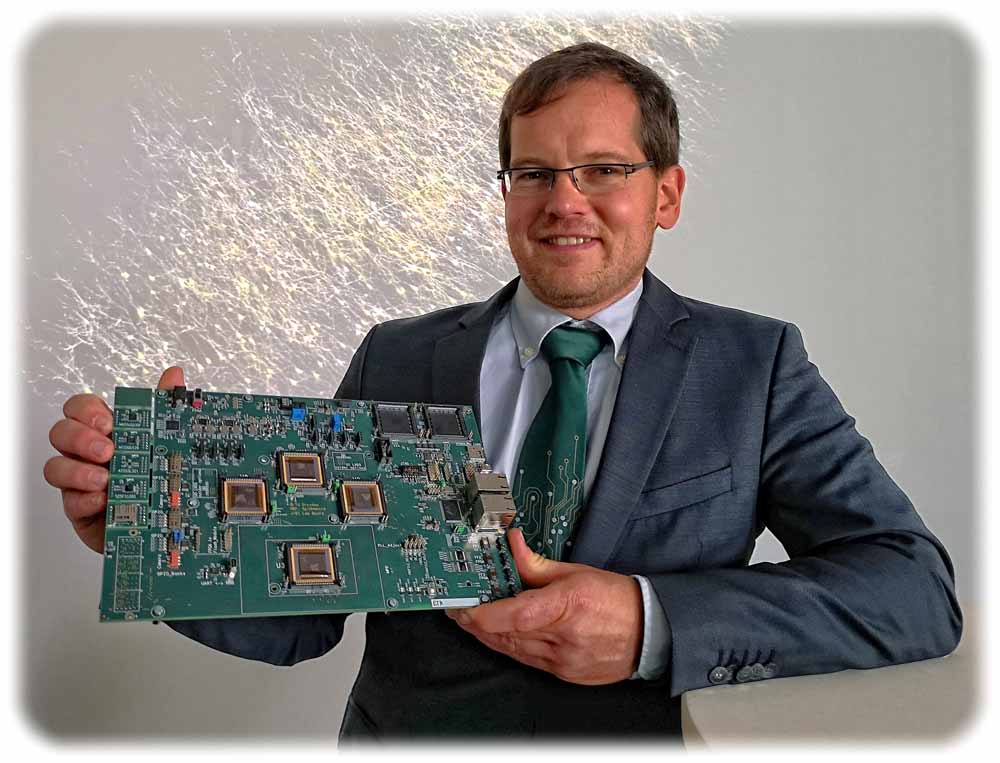

Die Archivaufnahme zeigt Professor Christian Mayr an der TU Dresden mit einer Platine, auf die Spinnaker2-Prototypenchips aufgelötet sind. Sie sollen die Neuronen im Gehirn simulieren. Foto: Heiko Weckbrodt

Hoffnung auf eine neue Prozessorschmiede

Parallel dazu arbeitet Prof. Christian Mayr an künstlichen Nachbauten neuronaler Netze. Außerdem waren und sind Dresdner Institute und Chipfirmen an Quantenprozessor-Projekten beteiligt. Besondere Hoffnungen verbinden sich seit einiger Zeit aber eben vor allem mit der RISC-V-Architektur, die – anders als manch ambitioniertes Entwicklungsprojekt – immerhin bereits anwendungsreif ist.

Als Aufbruchsignal in der Branche gilt in dieser Hinsicht eine Meldung von Bosch, Infineon, Nordic Semiconductor, NXP und Qualcomm: Die Chipkonzerne wollen in Deutschland eine gemeinsame RISC-V-Prozessorschmiede gründen. Und im Branchenverband „Silicon Saxony“ hofft man bereits, diese Neugründung womöglich in Dresden anzusiedeln: „Solch ein Unternehmen würde gut hierher passen“, hatte erst kürzlich Verbands-Geschäftsführer Frank Bösenberg im Oiger-Gespräch erklärt. Auch mit Blick auf die jüngsten Fortschritte im IPMS ist dieses Argument nicht von der Hand zu weisen.

Autor: Heiko Weckbrodt

Quellen: IPMS, Oiger-Archiv

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!

Du muss angemeldet sein, um einen Kommentar zu veröffentlichen.