Fraunhofer forscht an neuromorphen Speichern

Im europäischen Projekt „TEMPO“ wollen das IPMS und zahlreiche weitere Partner neuartige Hardware entwickeln, die sich konzeptionell an das menschliche Gehirn anlehnt

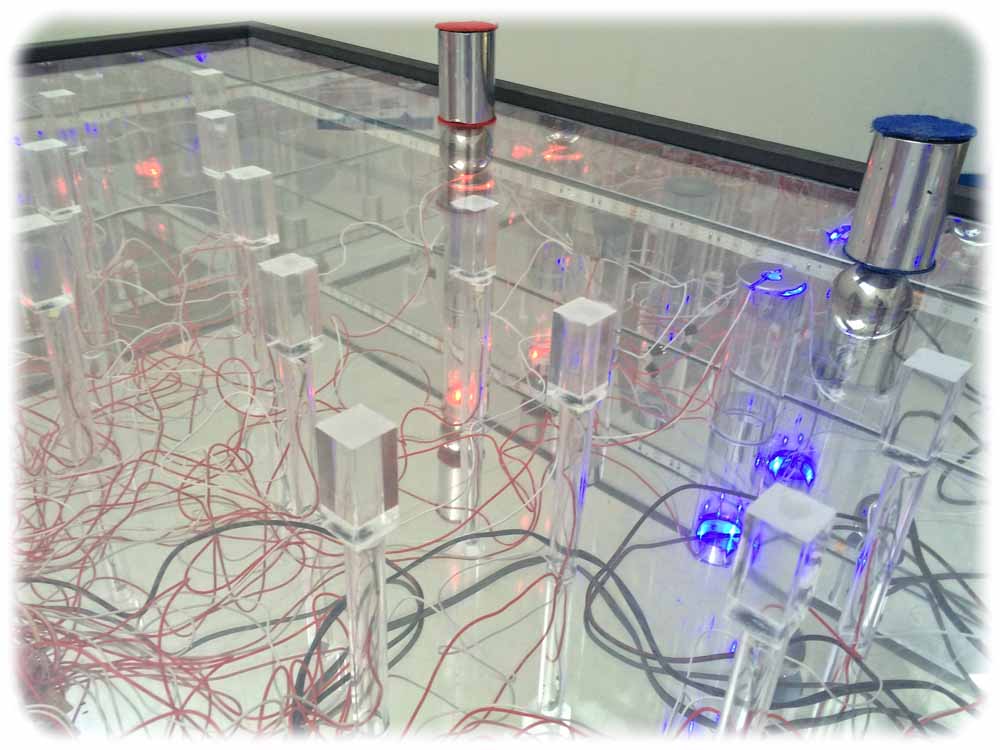

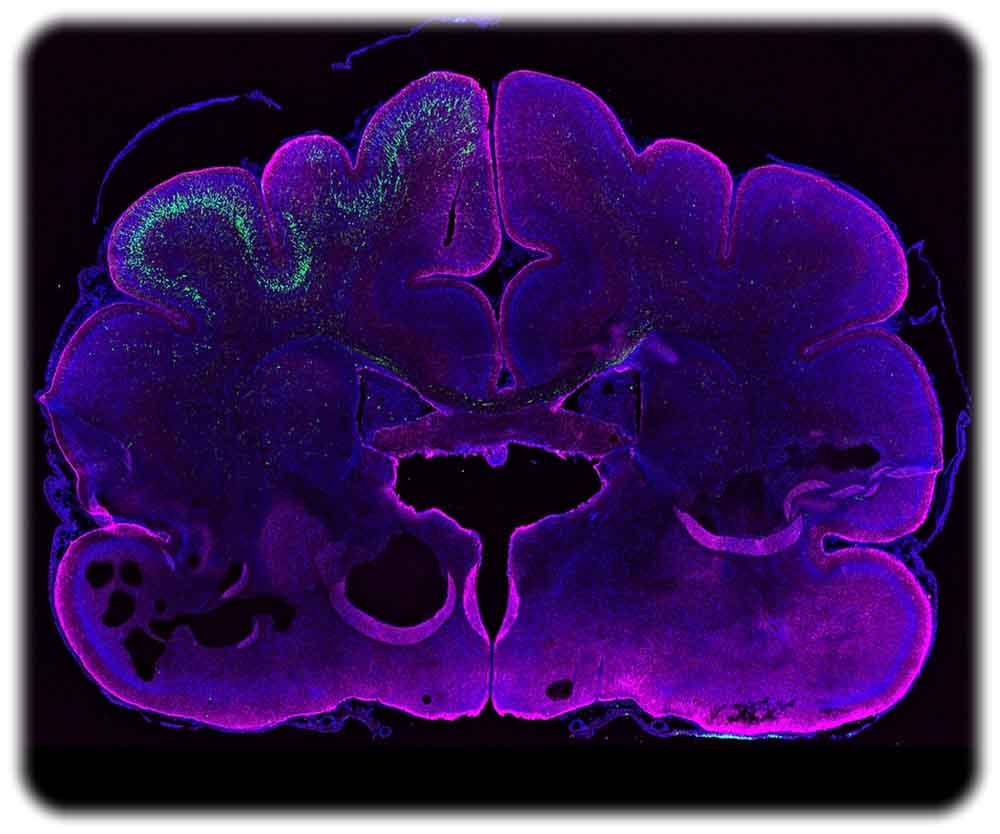

Dresden, 8. Februar 2018. Um die besonderen Fähigkeiten des menschlichen Gehirns künstlich nachzubilden, sind mehrere Wege denkbar. Einige davon wollen Forscher und Industrie-Ingenieure im Projekt „Technology & hardware for nEuromorphic coMPuting“ (TEMPO) ausloten, in dem sächsische Partner stark vertreten sind. Im Kern geht es darum, neuartige Computer-Hardware zu entwickeln, die sich eng an die Nervenzellen-Netzwerke des Hirns anlehnt.

„Entscheidend aus sächsischer Sicht ist, dass mit dem Projekt erste Schritte in Richtung der Entwicklung neuromorpher Chips durch neue Speicher erfolgen werden“, erklärte Martin Landgraf vom Fraunhofer-Institut für Photonische Mikrosysteme (IPMS), das sich maßgeblich beteiligen wird. Vieles deute darauf hin, dass „Neuromorphic computing“ ein Trendthema der nächsten zehn Jahre sein werde – und ein Schlüssel, um KIs stark zu verbessern und zum omnipräsenten Massenprodukt (AI of Everything = AIoT) weiterzuentwickeln

Dafür tun sich forschungsstarke und erfahrene Unternehmen und Institutionen zusammen. Dazu gehören das IPMS und weitere Fraunhofer-Institute, die Großforschungsinstitute IMEC und LETI aus Belgien und Frankreich, das Mayr-Team von der TU Dresden sowie die Unternehmen Infineon München, Bosch Reutlingen, Airbus Hamburg, Valeo Germany, Kortiq und Synergeticon. Gemeinsam beantragen sie derzeit Fördergelder aus dem ECSEL-Programm der EU für das Projekt „TEMPO“.

Ist Von Neumann ausgereizt?

Mit diesem finanziellen Rückhalt wollen sie mehrere Pfade des „Neuromorphic computings“ untersuchen. So ist geplant, Informationen analog in Multi-Level-Speichern analog abzulegen. In diesen Speichern sollen die Bauelemente mehrere Zustände – statt nur 0 und 1 wie im digitalen RAM – einnehmen können. Ein zweiter Weg wäre, die in der Von-Neumann-Architektur übliche strikte Trennung von Prozessor und Speicher aufzugeben und Speicherzellen nahe den Rechenwerken einzubetten. Dies könnte den Stromverbrauch senken und die Datenzugriffe beschleunigen. Ein noch radikalerer Ansatz ist der komplette Verzicht auf Logik-Transistoren im Prozessor: Die Rechenarbeit würde dann in den Speicherzellen stattfinden.

Mit allen drei Ansätzen wird sich das IPMS beschäftigen. „Bis die neuen multilevelfähigen Speicher mit neuen Designs der TU Dresden und auf FDX Technologie von Globalfoundries in Serie gehen, wird aber noch einige Zeit vergehen“, betonte Martin Landgraf – er rechnet mit fünf bis zehn Jahren. Schon etwas früher werde es möglich sein, Speicher in neuromorphe Chips nahe an den Rechnerkernen einzubetten.

Know-How-Schub für Sachsen

Neben technologischen Ergebnissen und konkreten Produkten rechnen die Partner auch mit mittelbaren Effekte für ganz Europa. Durch „TEMPO“ soll sich die Kooperation der wichtigsten Halbleiter-Unternehmen und der drei großen europäischen Mikroelektronik-Forschungseinrichtungen vertiefen – also von IMEC, LETI und der sächsisch dominierten „Forschungsfabrik Mikroelektronik Deutschland“ (FMD) von Fraunhofer. Dies könnte bis dahin gehen, dass diese Akteure Spezialanlagen untereinander austauschen, Investitionspläne abstimmen, gemeinsame Standards entwickeln und dergleichen mehr. Speziell die Sachen spekulieren darauf, durch „TEMPO“, das „Human Brain Project“ und ähnliche Programme erhebliches Know-how in den KI-Technologien zu akkumulieren – eine Voraussetzung, um auch in der nächsten Dekade in der obersten Liga mitzuspielen.

Autor: Redaktion

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!