Viertelmilliarde für Sachsens Mikroelektronik-Forschung

Fraunhofer will mit „Apecs“-Pilotlinien einen Wachstumskern für neue Chiplet-Technologien im Freistaat schaffen

Dresden/Chemnitz/Brüssel, 17. September 2024. Um Europas Rückstand in der 3D-Chiplet-Technologie aufzuholen und der sächsischen Mikroelektronik neue Perspektiven zu geben, wollen vier Fraunhofer-Institute für eine Viertelmilliarde Euro neue Pilotanlagen für die dreidimensionale Chip-Endmontage in Dresden und Chemnitz aufbauen. EU und Bund haben bereits grünes Licht für das Projekt „Advanced Packaging and Heterogeneous Integration for Electronic Components and Systems“ (Apecs) gegeben. Daher hat nun auch das sächsische Kabinett für 15 Millionen Euro Landesanteil lockergemacht. Das geht aus einer Mitteilung des Wissenschaftsministeriums in Dresden hervor.

Kabinett sichert 15 Millionen zu – und hofft auf „neues Level“ für sächsische Halbleiterforschung

„Mit Apecs bringen wir unsere Halbleiterforschung auf ein neues Level“, ist Wissenschaftsminister Sebastian Gemkow (CDU) überzeugt. „Parallel zu den aktuellen Milliarden-Investitionen von Infineon, Globalfoundries, Bosch oder TSMC wird der Aufbau von neuen Pilotanlagen den Mikroelektronikstandort Sachsen weiter entscheidend aufwerten.“

Nicht zuletzt sei die gesellschaftliche Rendite erheblich, hieß es von der Landesregierung: Einerseits löse Sachsen mit jedem Euro Eigenanteil weitere 17 investierte Euro von Bund und EU aus.

3D-Chip-Montage ist bisher eine Lücke in Sachsens Halbleiter-Industrie

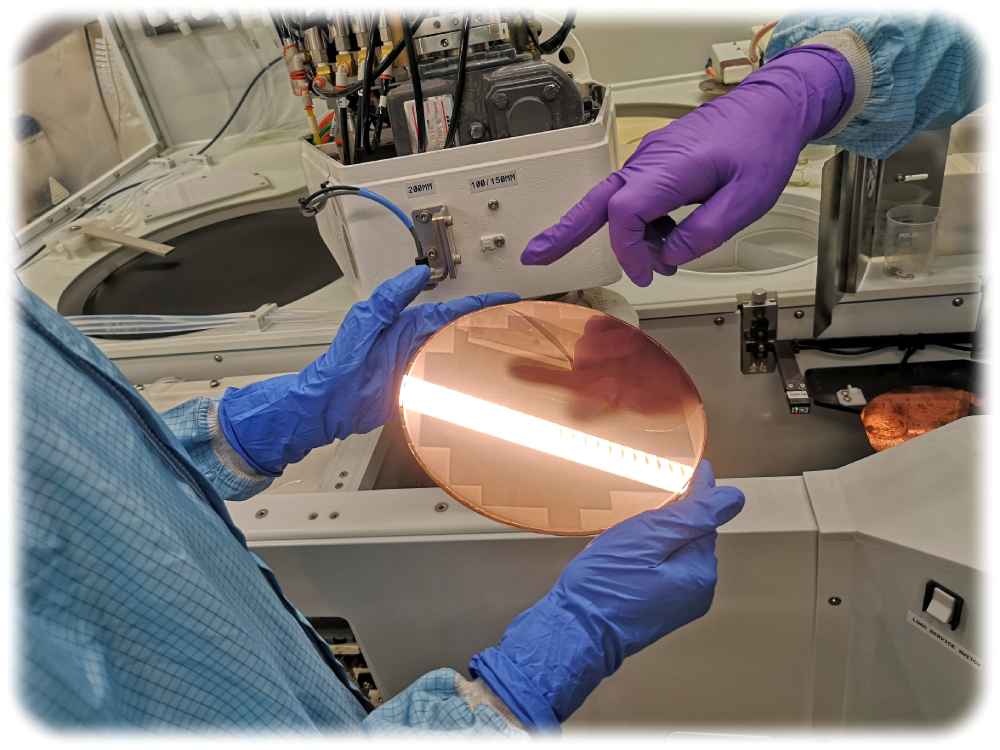

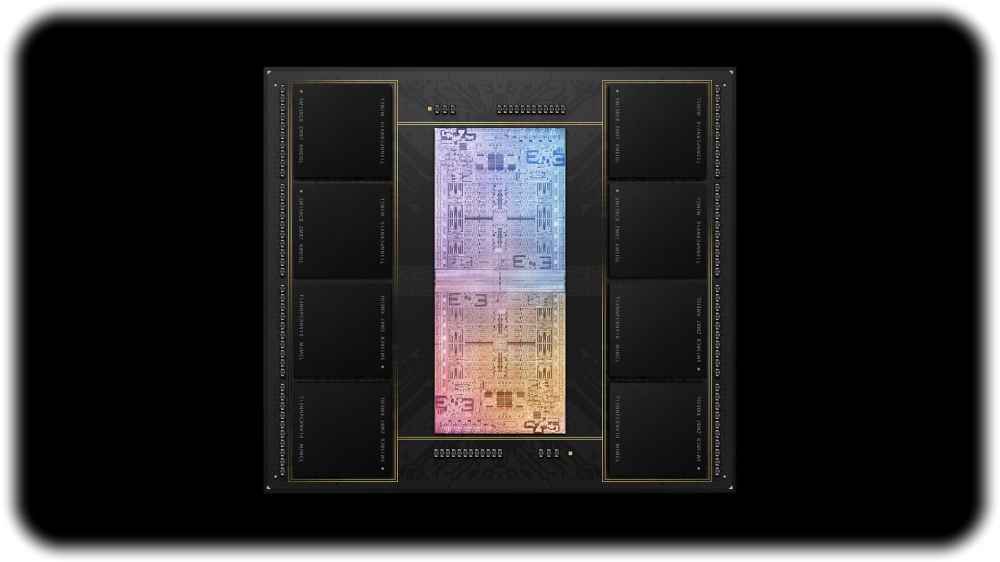

Anderseits dürfte die dieser noch junge Technologiepfad wichtige Lücken in der sächsischen Mikroelektronik-Wertschöpfungskette schließen: Die endet heute in der Regel mit dem „Frontend“-Prozess: einer fertig bearbeiteten und mit Chips versehenen Siliziumscheibe („Wafer). Die wird dann meist in speziellen Endmontage-Fabriken („Backend“) durchgetestet, zersägt, durchkontaktiert und mit Gehäusen versehen. Derweil verschwimmen allerdings gerade bei Marktführern wie TSMC in Taiwan und Samsung in Südkorea die Grenzen zwischen „Frontend“ und „Backend“: Sie verschmelzen Chips aus ganz unterschiedlichen Fertigungsprozessen, Integrationsgraden und teils auch aus unterschiedlichen Fabriken in „Chiplets“, die viele Funktionen auf kleinsten Raum packen – eine Art Nano-Legospiel.

Trendthema „Quasimonolithische Integration“ im Fokus

Der neueste Trend geht in Richtung „Quasimonolithische Integration“ (QMI). Dafưr erzeugen die Mikroelektroniker beispielsweise erst getrennt Speicherchips, Sensoren und Prozessorkerne, schleifen sie dann ganz dünn, fügen sie wie ein 3D-Puzzle in dünnen Stückchen übereinander und ziehen dann jeweils eine Begradigungsschicht ein, so dass die Siliziumscheibe danach wie ein ganz normaler Wafer weiterprozessiert werden kann.

Wafer und Chips werden bisher zwischen Europa und Asien hin und her kutschiert

Und eben solche Chiplet- und QMI-Prozesse wollen die Fraunhofer-Ingenieure in ihren Forschungs-Reinräumen und mit den neuen Pilotlinien zur Serienreife bringen. Denn das Interesse aus dem Automobilbau und anderen europäischen Industriezweigen an hochintegrierten Alleskönner-Mikrosystemen ist groß. Auch wäre es wünschenswert, wenn Europa nicht auf Gedeih und Verderben allein auf Zulieferungen aus Asien angewiesen wäre. Ganz abgesehen davon sind die Hin- und Her-Transporte von Wafern, Chips und Systemen zwischen Europa und Asien ökologisch suboptimal. Allerdings beherrschen eben Europas Chipfabriken diese fortgeschrittenen Chiplet- und QMI-Prozesse bisher nur ansatzweise. Immerhin formiert sich aber in Portugal mit den Amkor-Fabriken eine eigene Backend-Industrie auf dem Kontinent. Und gerade in Sachsen hatte vor allem der Fraunhofer-Institutsteil „Entwicklung Adaptiver Systeme“ (EAS) den Chiplet-Gedanken forciert und ein virtuelles Entwicklungszentrum dafür gegründet.

Europaweit sind 740 Millionen Chipgesetz für „Apecs“ geplant – 1/3 fließt nach Sachsen

Daher haben sich mehrere Institute aus ganz Europa zum Apecs-Verbund zusammengetan, darunter auch der Fraunhofer- und Leibniz-Verbund „Forschungsfabrik Mikroelektronik Deutschland“ (FMD). Angesichts der besonderen strategischen Bedeutung der geplanten „Fortgeschrittenen Packprozesse und heterogene Integration elektronischer Systeme und Komponenten“ hat die EU Sondersubventionen nach den Vorgaben des „Europäischen Chipgesetzes“ erlaubt. Das sieht neben direkten Milliardenförderungen für neue Halbleiterfabriken wie die von TSMC und Infineon in Dresden eben auch recht hohe Beihilfen für besonders wichtige Mikroelektronik-Pilotlinien vor.

Pilotlinien werden voraussichtlich im Ceasax Dresden und im Enas Chemnitz installiert

„Apecs“ ist als „paneuropäische Plattform“ konzipiert und umfasst europaweit ein Volumen von 740 Millionen Euro. Etwa ein Drittel davon – genauer gesagt 260 Millionen Euro – fließt nach Sachsen. Konkrete Pilotanlagen wollen hier das Fraunhofer-Institut für Elektronische Nanosysteme (Enas) in Chemnitz, das Fraunhofer Institut für Photonische Mikrosysteme (IPMS) Dresden, der Fraunhofer-Institutsteil „Entwicklung Adaptiver Systeme“ (IIS/EAS) Dresden und das das Zentrum „All Silicon System Integration Dresden“ (IZM-Assid) aus Boxdorf aufbauen. Die in Dresden geplante Anlagentechnik installieren die Fraunhofer-Forscher voraussichtlich im neuen „Zentrum für fortgeschrittene CMOS-Technologien und Heterointegration Sachsen“ (Ceasax) in Sichtweite zu den Fabs von Bosch und TSMC.

Autor: Heiko Weckbrodt

Quellen: SMWK, Oiger-Archiv, Wikipedia

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!