Die Physik der Elektronik-Fehler durchschauen

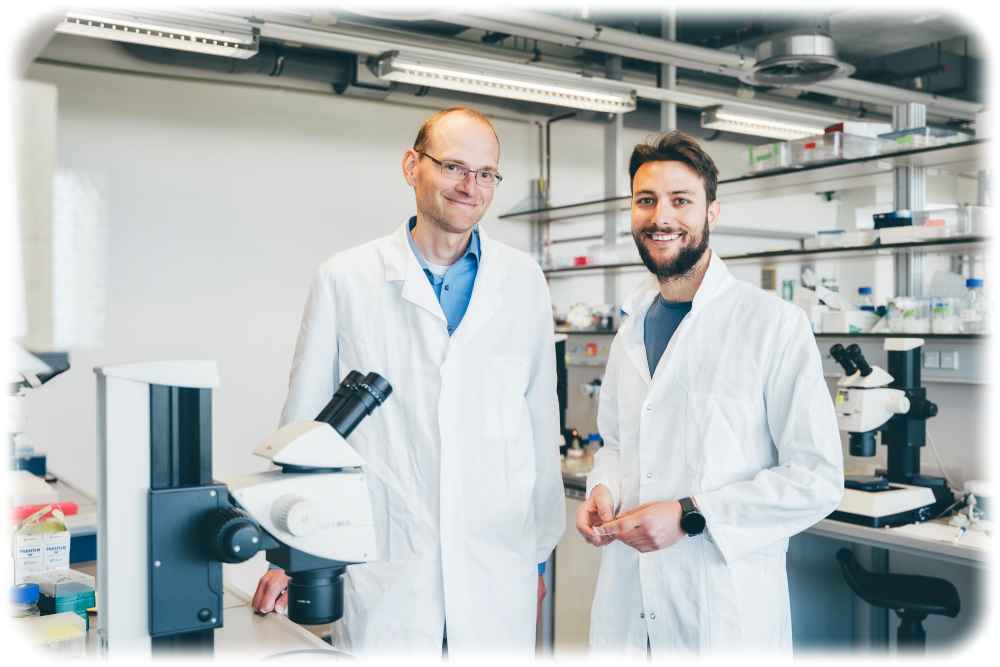

Fraunhofer-Experten vom EAS Dresden arbeiten an Simulationen, die beim Entwurf hochzuverlässiger Chips „Made in Europe“ helfen

Dresden, 17. März 2021. Um Schaltkreise „Made in Europe“ zuverlässiger zu machen, wollen Fraunhofer-Ingenieure aus Dresden den Chip-Entwurfsprogrammen eine „Fehlerphysik“ beibringen: Durch rasche Testläufe, die über eine künstlich simulierte Alterung der Schaltkreise hinausgehen, sollen Mikroelektronik-Designer künftig schon beim Entwurf spätere Ausfallrisiken erkennen können. Das geht aus einer Mitteilung des Fraunhofer-Institutsteils „Entwicklung Adaptiver Systeme“ (EAS) in Dresden hervor.

Künstliche Alterung im Computer war nur ein erster Schritt

„In heutiger Standard-Entwurfssoftware für integrierte Schaltungen sind zwar bereits Alterungssimulationen vorhanden“, räumt EAS-Projektleiter Dr. André Lange ein. „Allerdings verursachen sie noch einen enormen zusätzlichen Aufwand in den ohnehin bereits kritischen Verifikationsschritten.“ Deshalb wollen er und sein Team neue Zuverlässigkeits-Simulationen entwickeln, die bei der Entwicklung sehr robuster elektronischer Schaltkreise und Systeme helfen. In diese Programme wollen sie die „Physics of Failure“ einbetten: das Wissen und die Erfahrungen, welche physikalischen Mechanismen im Alltag häufig Fehler oder gar Totalausfälle in den Chips auslösen. Die Simulationen sollen schließlich in marktübliche Designsoftware-Pakete integriert werden.

Partner aus 12 Ländern an Initiative „iRel40“ beteiligt

Diese Forschungen am EAS sind Teil der europäische Forschungsinitiative „Intelligent Reliability 4.0“ (iRel40). „Die beteiligten Partner aus 13 Ländern wollen dafür die Zuverlässigkeit entlang der gesamten Wertschöpfungskette optimieren“, heißt es vom EAS. Das reiche „vom Wafer über den Chip und sein Package bis hin zum kompletten System“. Das EAS selbst gehört zum Fraunhofer-Institut für Integrierte Schaltungen (IIS).

Autor: hw

Quelle: EAS

Zum Weiterlesen:

Fraunhofer baut für 25 Millionen EAS-Komplex in Dresden

Fraunhofer will KI dem Mittelstand schmackhaft machen

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!