IDTechEx: Wenn Moore lahmt, kann 3D-Chip-Integration helfen

Analysten sehen hohen Bedarf für fortschrittliche Schaltkreis-Verpackungstechnologien – aber nur wenige beherrschen sie

Cambridge, 27. Mai 2023. Moderne 3D-Chipverpackungstechnologien sind im Kommen: Weil sich mikroelektronische Schaltungen auf herkömmlichen Wege nicht mehr beliebig weiter schrumpfen lassen, aber dennoch immer schnellere Computerchips für autonom fahrende Autos, Rechenzentren, Künstliche Intelligenzen und Konsumelektronik gebraucht werden, spielt die 3D-Integration mehrerer Chips in einem Schaltkreis in Zukunft eine immer größere Rolle. Das hat das britische Marktforschungs-Unternehmen „IDTechEx“ aus Cambridge prognostiziert.

Prognose: Unsere Zukunft ist datenzentriert

„Wenn wir unsere Zukunft mit einem Wort beschreiben würden, wäre es ,datenzentriert’“, schreiben das Analystenteam um Dr. Yu-Han Chang im Bericht „Fortschrittliche Halbleiter-Verpackungstechnologien: Der Entwicklungstrend und die Wachstumstreiber“. „Heutzutage gibt es auf allen Ebenen und in fast jeder Branche eine Datenexplosion. Jede Sekunde erzeugt unsere digitale Welt 4000 Terabyte an Daten, und es wird erwartet, dass diese Menge in Zukunft nur noch, wenn nicht sogar erheblich, ansteigt.“ Insofern nehme der Bedarf an immer leistungsfähigeren Prozessoren und anderen Schaltkreisen zu. Andererseits falle es der Mikroelektronik-Industrie jedoch immer schwerer, das sogenannte „Mooresche Gesetz“ noch einzuhalten und die Integrationsdichte monolithischer Computerchips noch alle zwei Jahre zu verdoppeln.

2,5D-Integration war nur ein Zwischenschritt

Dies dränge die Halbleiter-Industrie mehr und mehr dazu, „fortschrittliche Halbleiterverpackungen“ einzusetzen, meinen die Analysten. Gemeint ist damit: Vor etwa zehn Jahren begannen die Chiphersteller zunächst damit, mehrere Chips – zum Beispiel Prozessor, Speicher, Koprozessor oder Hochfrequenz-Einheit – in ein Chipgehäuse zu packen und dann zum Beispiel durch Drähte oder kleine Leiterbahnen zu verbinden. Diese „2,5D“-Integration war jedoch eher ein Kompromiss auf dem Weg zu einer echten 3D-Integration, bei der Chips auf der Wafer-Ebene dreidimensional (3D) miteinander verbunden werden, vor allem durch sogenannte „Through-Silicon Via“-Direktverbindungen (TSV). Damit ist inzwischen eine noch höhere Packungsdichte im Vergleich zu früheren Leiterplatten- oder 2,5D-Lösungen möglich.

Echte 3D-Integration auf Wafer-Ebene erfordert viel Prozess-Expertise

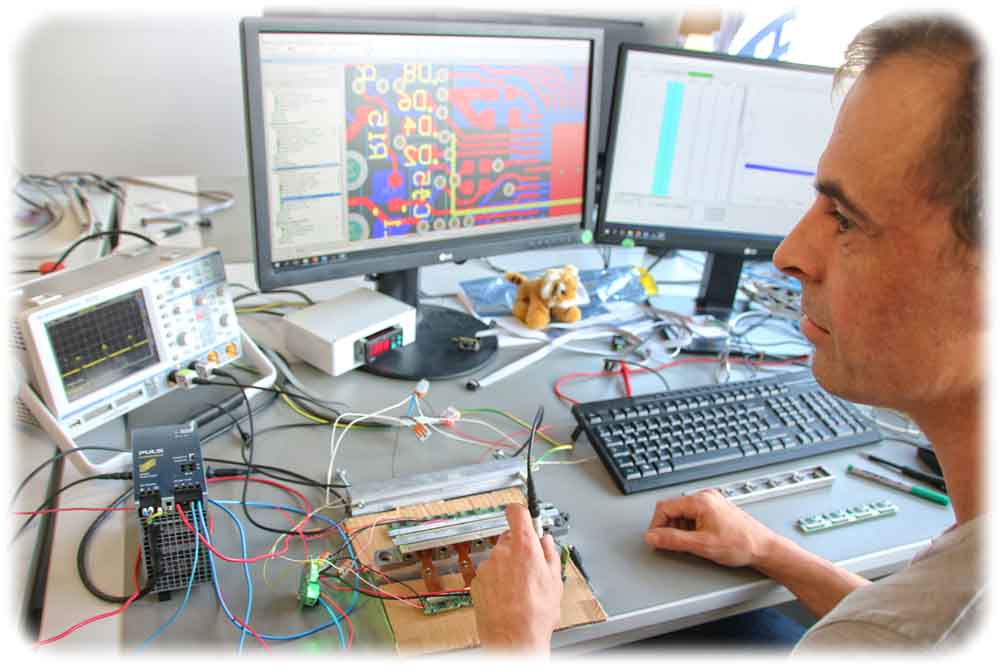

Allerdings sind solche 3D-Lösungen technologisch auch sehr anspruchsvoll und nur eine Handvoll Unternehmen beherrschen sie. Dazu gehören TSMC in Taiwan, Samsung in Südkorea und Intel in den USA. In Europa gibt es darüber hinaus Pilotlinien mit solchen TSV-Technologien, beispielsweise am Fraunhofer-Zentrum „All Silicon System Integration Dresden“ (Assid). Auch der Fraunhofer-Institutsteil für die „Entwicklung Adaptiver Systeme“ (EAS) beschäftigt sich mit 2,5- und 3D-Chipverpackungs-Technologien. Allerdings erfordert die 3D-Integration eben erhebliche Prozess-Expertise: Zwei Chips übereinanderzustapeln und zu kontaktieren, deren Kontaktkügelchen (Bumps) nur noch wenige Mikrometer auseinanderliegen, sei eine „erhebliche Herausforderung“ und erfordere eine „hochpräzise Ausrichtung“ und eine genaue Temperaturkontrolle, betonen die IDTechEx-Experten.

Nachfrage durch Rechenzentren, KI, autonome Autos und Smartphones

Wer diese Technologien aber in den Griff bekommt, kann auf jeden Fall auf erhebliches Marktpotenzial hoffen, meinen die Analysten: Sie sehen eine „steigende Nachfrage nach Datenverarbeitung als Hauptantriebskraft“ für eine wachsende Nachfrage nach 3D-integrierten Chiplösungen. Treiber seien unter anderem High-Performance-Computing-Anwendungen, KI-Technologien, Datenzentren, Kommunikationsnetzwerke, autonome Autos und Unterhaltungselektronik.

Sachsen will bei 3D-Integration aufholen

Auch in Sachsen bemühen sich Mikroelektronik-Forscher und Wirtschaftsförderer darum, in diesem Segment international Boden gut zu machen: Dafür bündelt Fraunhofer beispielsweise die Frontend- und Backend-Forschungskapazitäten von Assid und Nanoelektronikzentrum CNT in dem neuen „Center for Advanced CMOS & Heterointegration Technologies Saxony“ (Cachs). Außerdem versucht das EAS, in Sachsen ein Ökosystem für Chipendmontage, Chiplet-Technologien und 3D-Integration zu knüpfen. Und nicht zuletzt verbinden sich viele Hoffnungen im Freistaat mit einer möglichen Ansiedlung von TSMC: Wenn die Taiwanesen hier gemeinsam mit Partnern wie Infineon, Bosch und NXP eine Megafab bauen, wie der aktuelle Gerüchtestand besagt, dann könnte dies nicht nur die Kern-Chipproduktion im „Silicon Saxony“ auf eine neue Stufe heben, sondern in der nächsten Kaskade vielleicht auch wertvolles Knowhow zur 3D-Schaltkreis-Integration nach Sachsen spülen.

Autor: Heiko Weckbrodt

Quellen: IDTechEx, Oiger-Archiv

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!