„3D-Integration ist ganz große Chance für Europa“

Semi-Verband hat Europas Top-Mikroelektroniker zum „3D & Systems Summit 2025“ nach Dresden geholt

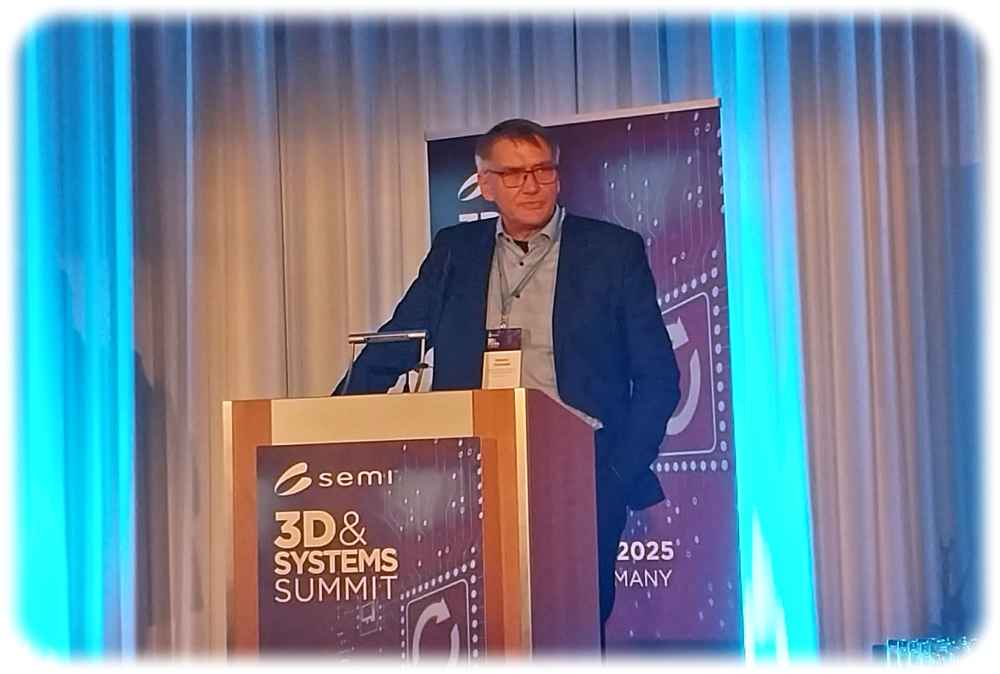

Dresden, 26. Juni 2025. Der Trend hin zu heterogenen 3D-Chips bietet Frankreich, Deutschland und anderen europäischen Ländern einzigartige Möglichkeiten, neue Positionen in der globalen Mikroelektronik zu besetzen. Das hat Direktor Sébastien Dauvé vom französischen Halbleiter-Großforschungszentrum „Cea Leti“ während der Konferenz „Semi 3D & Systems Summit 2025“ in Dresden prognostiziert: „Die 3D-Integration ist eine ganz große Chance für Europa.“

Europäer wollen ihre Stärken bei MEMS auf Chiplets übertragen

Der Grund für den Optimismus: In der Massenproduktion von Prozessoren und Speichern der neuesten Strukturgenerationen unterhalb von zehn Nanometern hat Europa zwar längst den Anschluss verloren und auch kaum Chancen, dies in naher Zukunft zu ändern. Doch viele europäische Unternehmen und Institute haben starke Marktpositionen in der Automobilelektronik, vor allem aber beim Entwurf und der Produktion „Mikroelektromechanischer Systeme“ (Mems), die dann in Smartphones, Fahrzeugen, Industrierobotern oder anderen Technologie-Erzeugnissen als Druckmesser, Gassensor, Mikro-Lautsprecher, Mikrophon, Ortungssystem, Miniatur-Kreiselkompass und dergleichen mehr dienen. Diese Stärken mit Chipfabriken, die Europa ohnehin verfügbar sind, in die Chiplet-Technologie zu übertragen, würde ganz neue Leistungsklassen, Integrationsgrade und Kostenvorteile für derartige Universalkönner „Made in Europe“ möglich machen.

Leti-Pilotlinie soll FD-SOI-Technik stärken, Imec setzt bei NanoIC auf 2-nm-Technologien

Von daher möchten Cea-Leti und die deutschen Fraunhofer-Mikroelektroniker nun ein Missverständnis ausräumen, das mit den jüngsten Chipgesetz-Zuschüssen aufgekommen war: Abgesehen vom Projekt „NanoIC“ im belgischen Imec, das sich in der Tat auf 2-Nanometer-Chipstrukturen fokussiert, zielen die Milliarden-Zuschüsse für „Pilotlinien“ gar nicht so sehr darauf, den europäischen Rückstand zu TSMC, Samsung, Intel und anderen Sub-10-Nanometer-Technologieführern verringern – und dabei zwangsläufig mangels Erfahrung und Kapital zu scheitern, wie viele Branchenbeobachter fürchten.

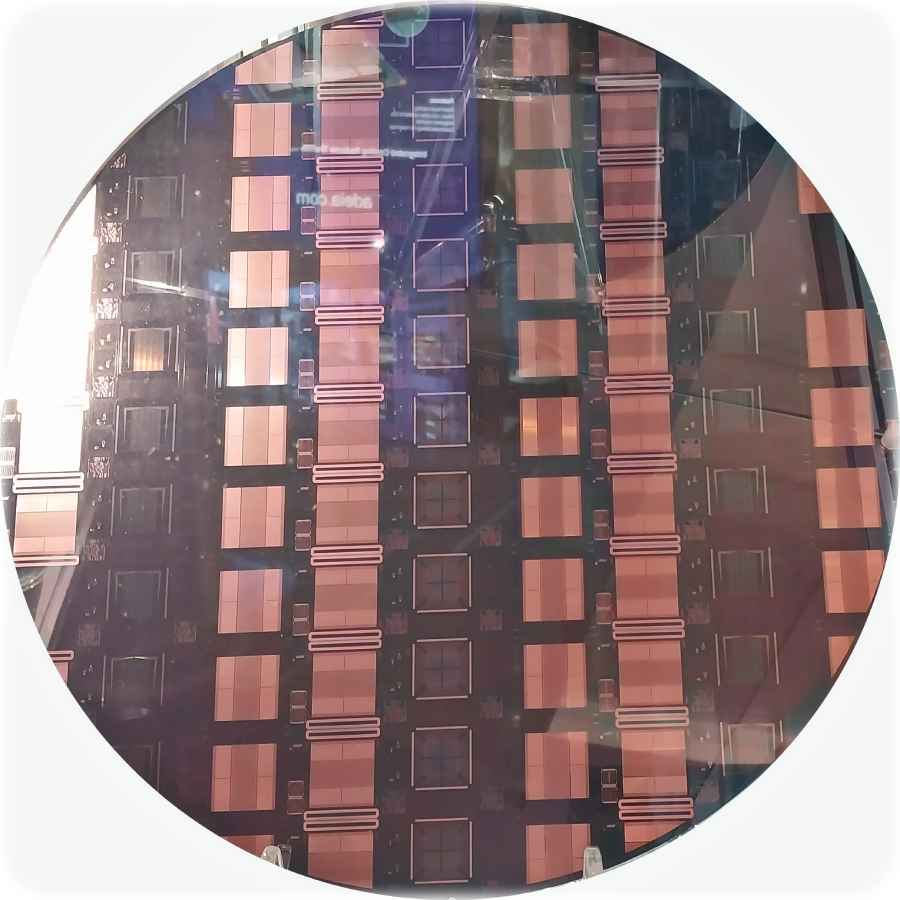

Apecs wird zu großen Teilen in Sachsen realisiert – und zielt auf heterogene 3D-Chiplets

Vielmehr sollen die geplanten Pilotlinien „Apecs“ in Sachsen und ganz Deutschland, die französische „Fames“-Linie und das belgische „NanoIC“-Projekt bestehende Stärken stärken und wichtige Lücken in der Wertschöpfungskette schließen. So wollen die Franzosen in Grenoble beispielsweise ihre FD-SOI-Chiparchitektur auf die nächste Stufe heben, optisch-elektrische Signalkoppler, neuartige merkfähige Speicherzellen wie FeRAM, MRAM und oxRAM integrieren – zum Beispiel für neuromorphe Schaltkreise – sowie das „direkte hybride Bonding“ vorantreiben. Letztere Technologie beruht darauf, fertiger Wafer oder Chips passgenau übereinander zu pressen, sie auf einige Hundert Grad zu erhitzen und dann auf molekularer Ebene miteinander elektrisch zu verschweißen beziehungsweise durchzukontaktieren. Auch dies dürfte die Packungsdichte mikroelektronischer Systeme noch einmal deutlich zu erhöhen.

Europa setzt auf Lego-Baukasten aus Prozessoren, Speicher, Sensoren, Photonik, organischer Elektronik und Antennen

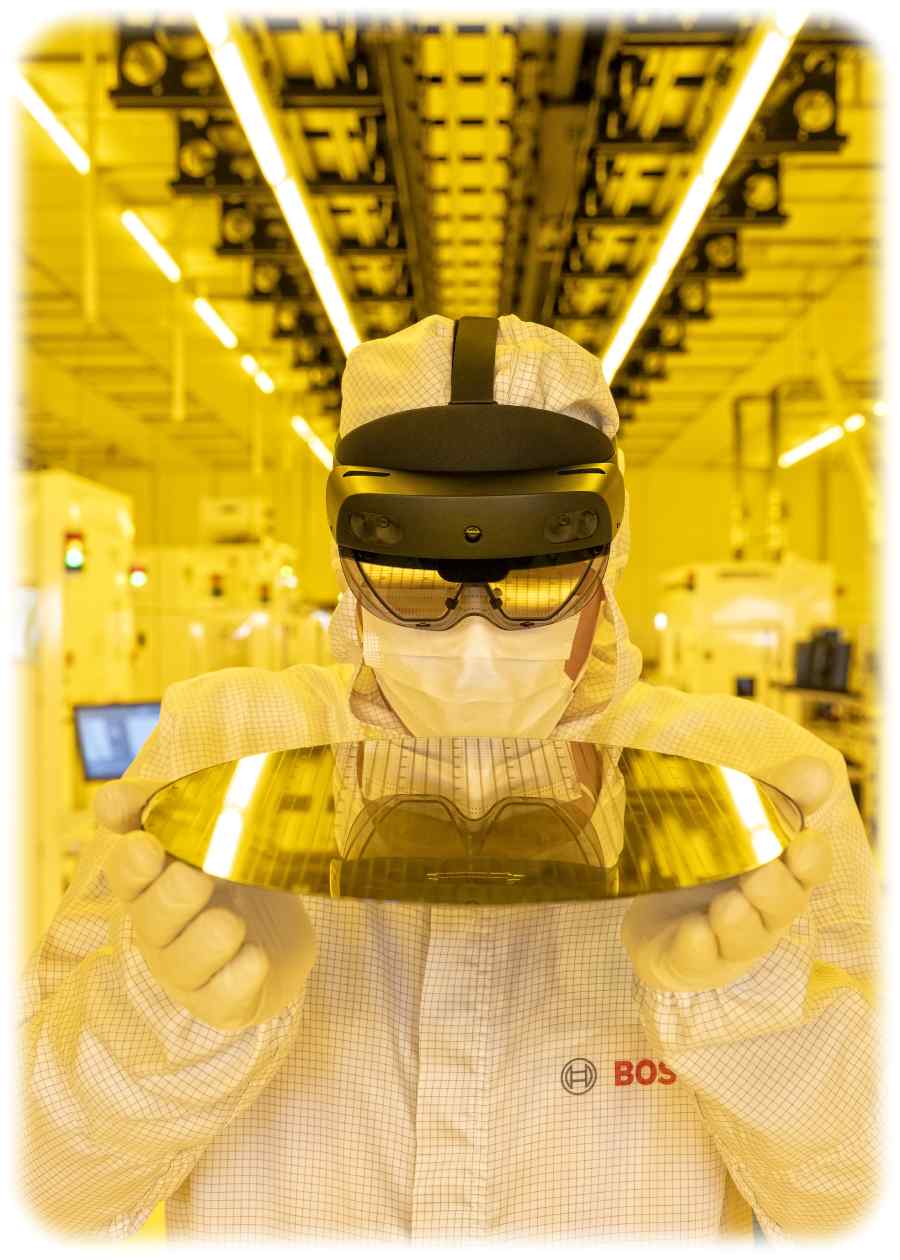

Die Pilotlinie „Advanced Packaging and Heterogeneous Integration for Electronic Components and Systems“ (Apecs) wiederum, die Fraunhofer zu erheblichen Teilen in Dresden und Chemnitz aufbauen will, soll Chiplet-Technologien eine neue Richtung geben: hin zu einer „quasi-monolithischen Integration“ (QMI) von Chiplets zu einem Ganzen, das von einem Chip kaum noch zu unterscheiden ist, der „in einem Guss“ gefertigt wurde. Das Besondere dabei sind die geplanten Teilkomponenten: Während TSMC & Co. vor allem Rechnerkerne, Speicher und Beschleuniger kombinieren, wollen die Europäer dem „Legokasten“ auch Sensoren, Photonik, organische Elektronik, Antennen und andere heterogene Bausteine hinzufügen. „Das wird der Chiplet-Technologie eine ganz neue Qualität geben“, ist Stephan Guttowski von der federführenden „Forschungsfabrik Mikroelektronik Deutschland“ (FMD) überzeugt. Aufhorchen ließ auf der Konferenz zudem seine Ankündigung, bisher in Europa fehlende Testkapazitäten für 3D-Chips im Zuge von „Apecs“ aufzubauen und europäischen Firmen und Instituten zugänglich zu machen. „Das benötigte Test-Equipment ist allerdings sehr teuer und braucht sehr erfahrenes Personal“, räumt Guttowski ein. Daher müsse er diese Kapazitäten bündeln.

Heterogene Bauweise birgt Vergiftungsgefahr

Zudem sieht der FMD-Chef noch eine Reihe von Herausforderungen auf die Apacs-Partner zukommen, wenn sie die heterogene und quasi-monolithische 3D-Integration in den Griff bekommen wollen: Letztlich müssten dabei klassische CMOS-Bauteile, Indiumphosphid- und Galliumarsenid-Chips, siliziumbasierte Photonik und viele ganz artfremde Materialien in einem Komplex kombiniert werden, ohne einander zu stören oder zu „vergiften“.

Großer Sprung nach vorn erwartet

Allerdings sieht Guttowski auch erhebliche Marktchancen und viele Applikatonen aus dieser neuen Chiplet-Generation erwachsen. Als Demonstratoren wollen die Apecs-Partner beispielsweise hochintegrierte Auto-Schaltkreise, Elektronik für Medizintechnik, Industrie-Schaltkreise fertigen, aber auch beim Thema Hochleistungs-Chips für Rechenzentren einen Sprung vorwärts machen: Durch die dichte Integration von optischen Datenverbindungen, die Durchsätze von 800 Gigabit je Sekunde (Gbs) und mehr schaffen, mit KI-Beschleunigern, ferroelektrischen Neuro-Speichern, neuen Rechenwerken und anderen heterogenen Komponenten lassen sich womöglich HPC-Schaltkreise bauen, die es mit denen von Nvidia & Co. aufnehmen können – so die Hoffnung.

Autor: Heiko Weckbrodt

Quellen: Semi 3D Summit, FMD, Cea-Leti, Oiger-Archiv, Wikipedia

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!