makeChip soll auch kleinen Butzen eigene Chips ermöglichen

Dresdner Studio stellt Entwurfssoftware für Globalfounries FD-SOI-Technologie vor

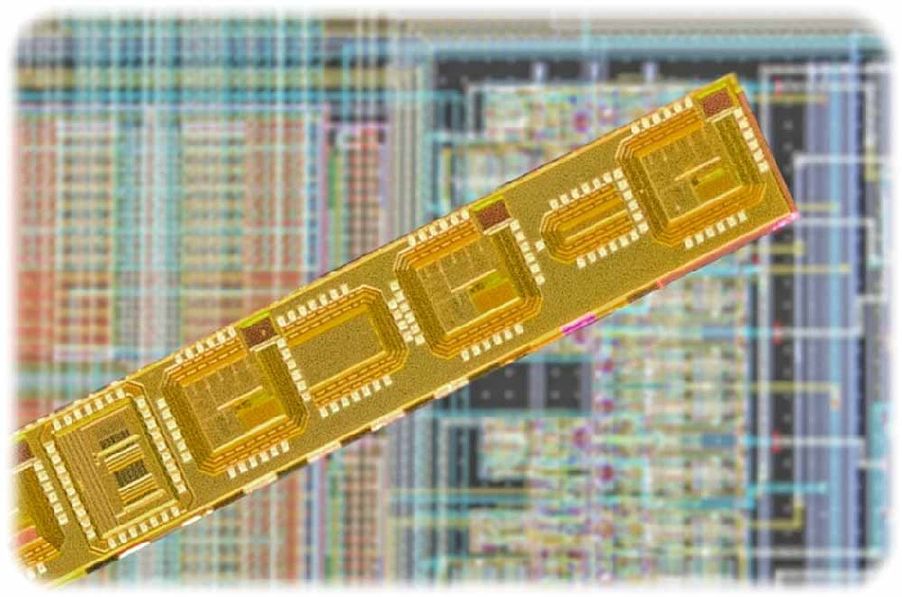

Dresden, 10. Mai 2017. Um kleinen und mittleren Unternehmen den Entwurf eigener Computerchips zu erleichtern, hat das Dresdner Unternehmen Racyics nun das Design-Programm „makeChip“ für die 22FDX-Halbleitertechnologie von Globalfoundries (GF) vorgestellt. Das teilten Globalfoundries Dresden und Racyics heute mit.

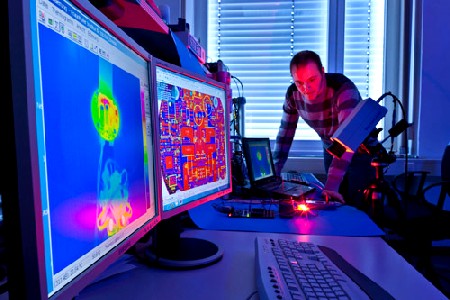

„Wir wollen es Start-Ups, kleinen und mittleren Unternehmen sowie der akademischen Welt ermöglichen, ganz vorn mit dabei zu sein“, betonte Racyics-Chef Holger Eisenreich in einer gemeinsamen Mitteilung mit Globalfoundries Dresden. makeChip erlaube ihnen „einen schnellen und kosteneffizienten Einstieg in den Analog-/Mixed-Signal- und Digitalschaltungsentwurf auf Basis von GFs 22FDX-Technologie, um Mikrochips für IoT- und Industrie-4.0-Anwendungen zu entwickeln“.

makeChip werde auch von dem branchenüblichen Chipdesign-Programm „Cadence“ unterstützt. Für alle nicht-kommerziellen akademischen Projekte soll das Programm kostenfrei nutzbar sein.

Racyicswurde 2003 von Mitarbeiters der TU Dresden gegründet. Das Unternehmen hat derzeit rund 30 Mitarbeiter und ist auf komplette Systeme auf einem Chip (SoC) spezialsiert. hw

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!