Fraunhofer Dresden vervierfacht Tempo von 3D-Chips

400 Gigabit je Sekunde für Kamera-Speicher

Dresden, 15. Februar 2016. Fraunhofer-Wissenschaftler aus Dresden haben gemeinsam mit dem Unternehmen „Dream Chip Technologies“ im Projekt „Memory3“ einen 3D-Chip für hochauflösende Kameras entwickelt, der Bild-Daten viermal so schnell wie frühere Modelle hin- und her schaufeln kann. Der Chip erreicht dabei Datentransfer-Raten bis zu 400 Gigabit je Sekunde (Gbs). „Für die Elektronik von Ultra-HD-Kameras und andere leistungsintensive Bauteile kommt die neue, dreidimensionale Integrationstechnologie einem Quantensprung gleich“, schätzten die Forscher des Dresdner Institutsteils Entwurfsautomatisierung (EAS) im Fraunhofer-Institut für Integrierte Schaltung (IIS) ein.

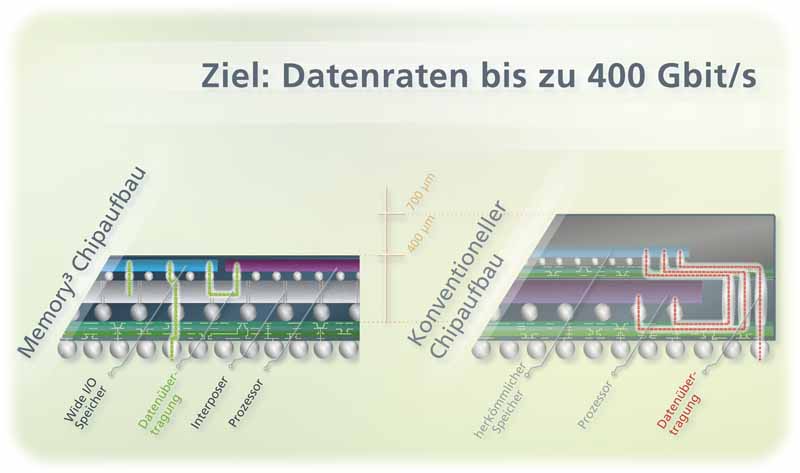

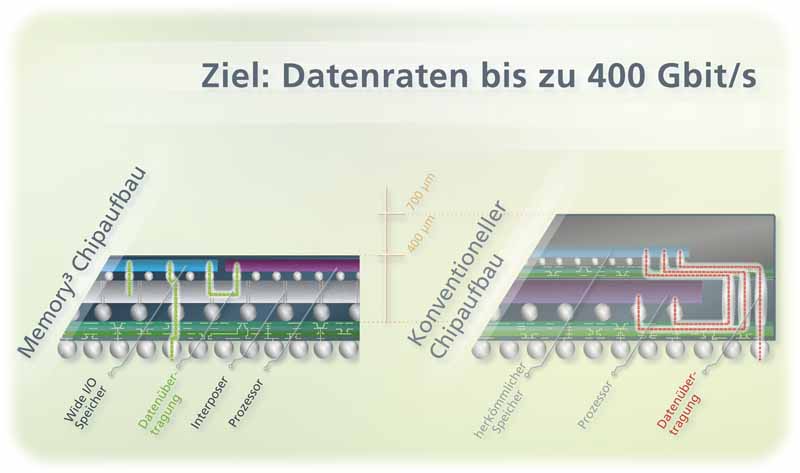

Oft werden Kombi-Chips erzeugt, indem Prozessor und Speicher nur übereinander gestapelt und außen elektrisch verbunden werden. Für „Memory3“ hingegen ordnete das Team um Gruppenleiter Andy Heinig Prozessor und Speicher sind im selben Gehäuse an und verband beide durch eine dünne Datenleitungs-Schicht (Interposer). Durch diese hochfeine Leitungsstruktur können Prozessor und Speicher so dicht „zusammenwachsen“, dass sich der Datenaustausch deutlich beschleunigt und der Energieverbrauch senkt, hieß es vom EAS. „Lag der Abstand zwischen den Chips ursprünglich im Millimeterbereich, arbeiten wir nun deutlich unter einem Millimeter“, betonte Heinig.

Der Fraunhofer-Experte sieht gute Chancen, mit diesem technologischen Ansatz die Datenraten künftiger 3D-Chips noch einmal zu vervierfachen. Auch erscheine ein Einsatz jenseits der Kameraindustrie, zum Beispiel bei Grafikkarten oder Vermittlungsknoten von Glasfasernetzen sinnvoll.

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!