Einen Einsatzzweck für den Grafikprozessor Tesla100 („Pascal“) sieht Nvidia in der Entwicklung Künstlicher Intelligenz. Foto: Nvidia

Nvida packt fast 4000 Rechner-Kerne in einen Prozessor

Santa Clara, 10. April 2016. Der Trend, immer mehr Rechenkerne auf jeden Prozessorchip zu packen, setzt sich fort. So hat das kalifornische Grafikprozessor-Unternehmen Nvidia mit der „Pascal“-Porozessorarchitektur nun einen Tesla-100-Chip mit 3840 Rechnerkernen entwickelt. Solche Vielkern-Prozessoren eignen sich besonders, um aufwendige Berechnungen parallel abzuarbeiten – zum Beispiel in Verkehrssimulationen, für Künstliche Intelligenzien oder bei der Vernetzung vieler Geräte im „Internet der Dinge“.

Für die richtig interessanten IoT-Szenarien brauchen wir richtig schnelle Chips

Dieses „Internet of Things“ (IoT), also die Vernetzung aller möglichen technischen Geräte untereinander und mit den Menschen, braucht ständig höhere Rechnerleistungen. Zwar gibt es auch einfache Aufgaben, die von billigen Chips im Internet der Dinge bewältigt werden können. Dazu gehört zum Beispiel in sogenannten „Smart Homes“ die Kommunikation zwischen Herd und Heizung oder zwischen Lichtdetektor und Jalousien, um die Heizung oder Kühlung zu optimieren. Aber die wirklich interessanten Anwendungen, die auch eine neue Qualität der ubiquitären (allgegenwärtigen) Elektronik darstellen, wie etwa für autonom fahrende Autos, für künstliche Intelligenz, für die „Virtual Reality“, 3-Graphiken oder für das „Deep Learning“, wo Geräte mit den gleichen Methoden wie Menschen lernen, werden wesentlich höhere Rechnerleistung als bisher auf kleinstem Raum (also keine Großrechnerzentren) benötigt.

Durch Reaktionszeiten unter 1 Millisekunde soll die 5. Mobilfunk-Generation („5G“) imstande sein, Dutzende, ja Hunderte Roboterautos so miteinander zu vernetzen, dass Zusammenstöße nahezu ausgeschlossen sind und viel Straßen-Neubau wegfallen kann – weil die Pisten dann dichter mit schnell fahrenden Autos „gepackt“ werden können. Die Koordination sollen winzige Supercomputer mit Millionen Rechnerkernen übernehmen, die bis 2030 an der TU Dresden entwickelt werden sollen. Foto (bearbeitet): Heiko Weckbrodt

Pascal schafft bis zu 21 Billionen Operationen je Sekunde

Die kalifornische Firma Nvidia hat hier jüngst einen Durchbruch erzielt. Sie haben einen Rechnerbeschleuniger (Tesla P100) für die oben genannten Anwendungen mit einem Aufwand von zirka 3 Milliarden Dollar entwickelt, dessen Kernstück der neue Grafikprozessor GPU 100 („Pascal“) ist. Dieser Super-Chip enthält fast 4000 Rechnerkerne, aufgebaut aus rund 15 Milliarden Transistoren und erreicht eine Rechnergeschwindigkeit von bis zu 21 Tera-Flops (21 Billionen Fließkomma-Operationen pro Sekunde). Hergestellt wird der bereits in Produktion befindliche Grafikprozessor beim taiwanesischen Auftragsfertiger TSMC in 16-Nanometer-Technologie. Der Chip ist stolze 610 Quadratmillimeter groß.

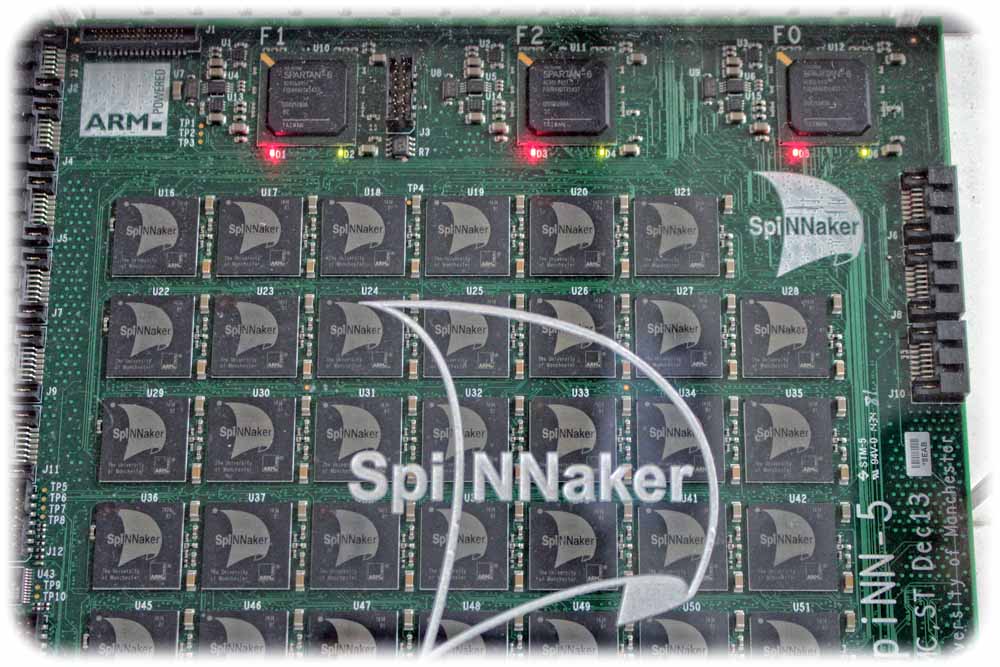

Die SpiNNaker-Neurocomputer beruhen auf ARM-Prozessoren mit sehr vielen Kernen, die bei Globalfoundries produziert werden und auf denen die künstlichen Neuronen per Software simuliert werden. Die aktuelle Generation kommt an die Leistungsklasse von Tiergehirnen heran. In naher Zukunft wollen die Dresdner Forscher damit aber in die Klasse der Menschengehirne vorstoßen. Foto: Heiko Weckbrodt

Hunderttausende Kerne für Neurocomputer und Roboterautos benötigt

Um künftig noch leitungsfähigere Chips für das Internet der Dinge zu produzieren werden noch kleinere technologische Prozessgeometrien als 16 Nanometer benötigt, damit solche Chips wirtschaftlich gefertigt werden können. Experten gehen in Zukunft von einem Bedarf von über 100.000 Rechnerkernen pro Chip aus. An solchen Konzepten arbeiten derzeit beispielsweise auch Neurocomputer-Entwickler an der TU Dresden, um gehirnähnliche Rechner zu entwickeln. Ähnliche Multikern-Ideen verfolgen auch ihre Kollegen vom 5G Lab Germany an der TU Dresden, sie wollen die Vielkerner aber vor allem für eine intelligente Verkehrssteuerung von Roboterautos einsetzen. Und Mikroelektronik-Branchenprimus Intel verfolgt bereits seit vielen Jahren Vielkern-Prozessorkonzepte.

Autoren: Bernd Junghans und Heiko Weckbrodt

Zum Weiterlesen:

5G-Forscher wollen Supercomputer im Tetrapack-Größe

TU-Experten wollen Neurocomputer wie ein Menschenhirn bauen

Was ist eigentlich Industrie 4.0?

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!