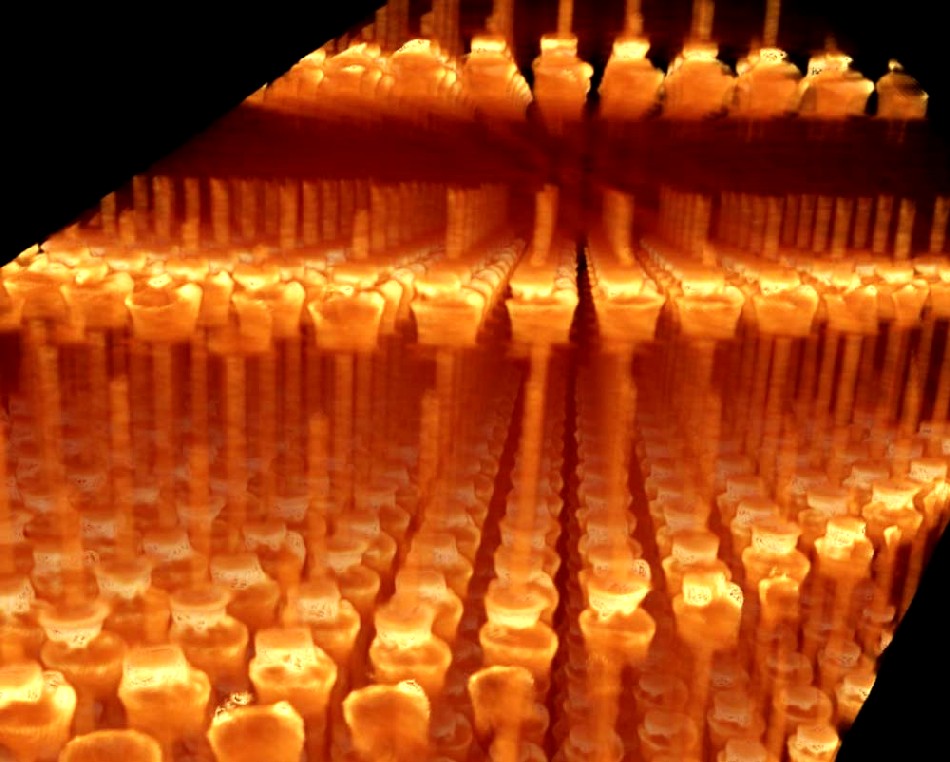

3D-Chips: Hoffnungsträger für Europas Nanoelektronik

Dresden setzt auf Halbleiter-Konstruktion im Raum statt nur in der Fläche Dresden, 11. April 2015: Mit neuen Chiparchitekturen, die 2D- und 3D-Elektronikkonstruktionen kombinieren, könnte Europa im weltweiten Standortwettbewerb deutlich punkten – und hat dafür inzwischen auch gute Chancen. Das hat Professor Ehrenfried Zschech vom Dresdner Zentrum für Nanoanalyse (DCN) im Vorfeld der internationalen Elektronik-Tagung „Frontiers of Characterization and Metrology for Nanoelectronics“ (FCMN) eingeschätzt, die am 14. April 2015 in Dresden beginnt. „In der 3D-Integration wird sich Europa positionieren können und für den Halbleiter-Standort Dresden sehe ich da besonders gute Entwicklungsmöglichkeiten“; sagte er im Oiger-Gespräch.“