Fraunhofer baut Chip-Forschungszentrum Ceasax in Dresden aus

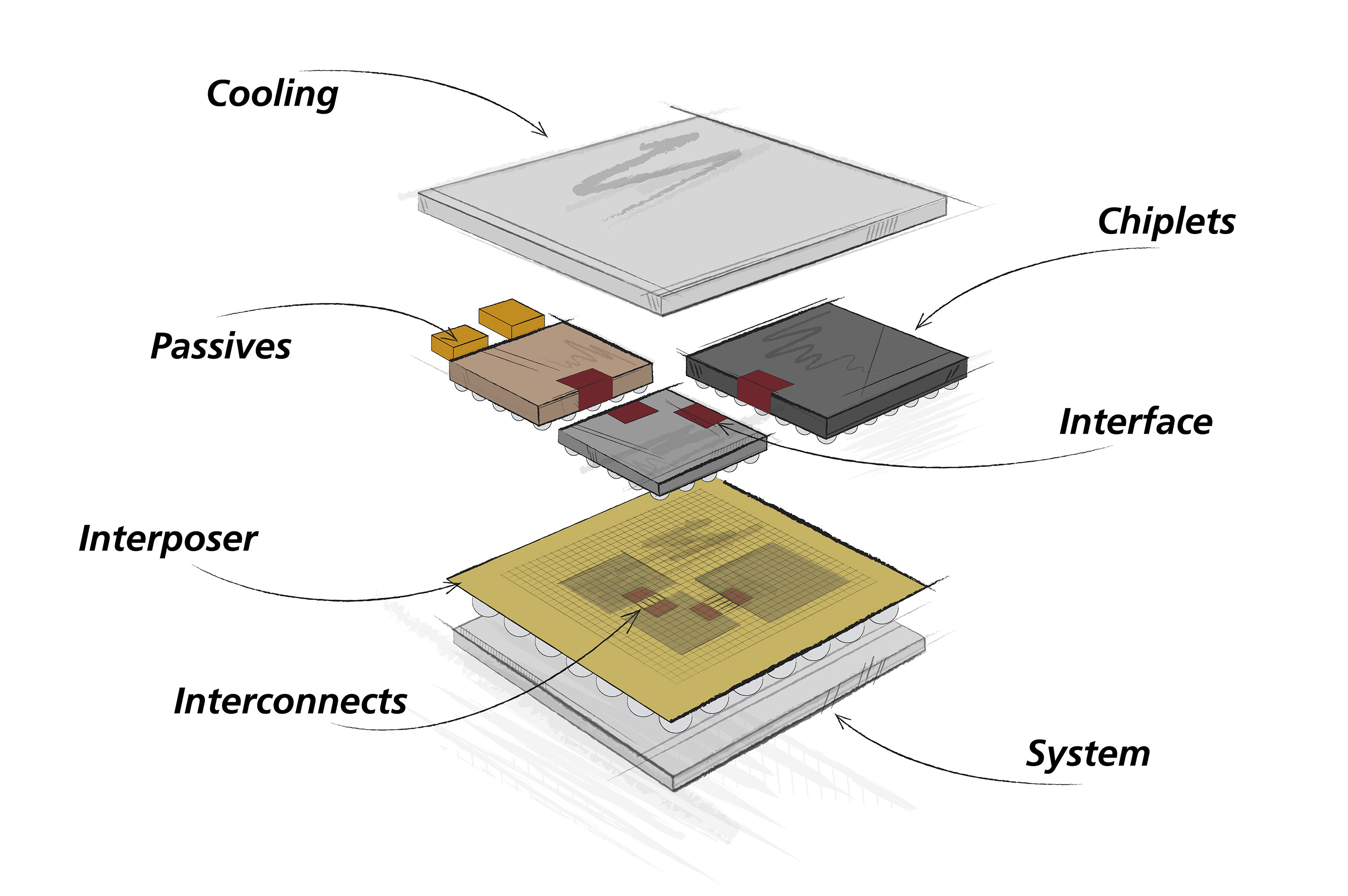

Neubau soll Platz für Zukunftsprojekte mit Sachsens Halbleiterindustrie schaffen Dresden, 31. Januar 2024. Kaum eröffnet, baut Fraunhofer sein noch junges Mikroelektronik-Forschungszentrum „Center for Advanced CMOS & Heterointegration Saxony“ (Ceasax) im Dresdner Norden auch schon wieder aus. Der Erweiterungsbau An der Bartlake – in Sichtnähe zu Bosch, dem Chipmaskenzentrum AMTC und dem Baugrund für die kommenden TSMC-Chipfabrik – ist bereits rohbaufertig. Das Zusatz-Gebäude soll die Forscher für neue Projekte gemeinsam mit der expandierenden sächsischen Halbleiter-Industrie wappnen.