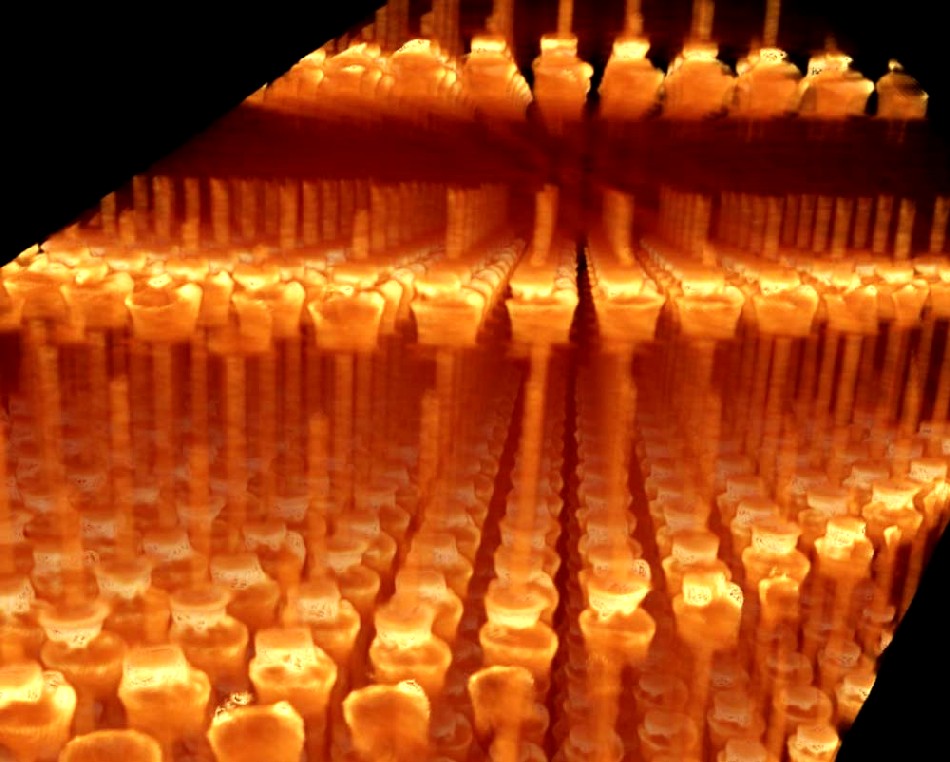

Röntgentomografie eines vertikal durchkontaktierten 3D-Chipstapels aus Dresden. Abb.: DCN, TU Dresden

Dresden setzt auf Halbleiter-Konstruktion im Raum statt nur in der Fläche

Dresden, 11. April 2015: Mit neuen Chiparchitekturen, die 2D- und 3D-Elektronikkonstruktionen kombinieren, könnte Europa im weltweiten Standortwettbewerb deutlich punkten – und hat dafür inzwischen auch gute Chancen. Das hat Professor Ehrenfried Zschech vom Dresdner Zentrum für Nanoanalyse (DCN) im Vorfeld der internationalen Elektronik-Tagung „Frontiers of Characterization and Metrology for Nanoelectronics“ (FCMN) eingeschätzt, die am 14. April 2015 in Dresden beginnt. „In der 3D-Integration wird sich Europa positionieren können und für den Halbleiter-Standort Dresden sehe ich da besonders gute Entwicklungsmöglichkeiten“; sagte er im Oiger-Gespräch.“

Europa in spielt in weltweiter Mikroelektronik bisher nur 2. (oder 3.) Geige

Solch eine Spezialisierung auf die noch junge 3D-Chiptechnik könnte möglicherweise helfen, Europas Anteil an der weltweiten Halbleiterproduktion spürbar zu erhöhen. Der liegt derzeit bei nur rund 6 %, soll aber nach dem Willen der EU-Kommission in naher Zukunft auf 20 % steigen. Impulse könnten dabei von den Dresdner Forschungen ausgehen.

3D-Cluster im TU und Fraunhofer entstanden

Denn in der sächsischen Landeshauptstadt ist in den vergangenen Jahren ein 3D-Elektronik-Forschungsverbund vor allem aus Fraunhofer– und TU-Instituten sowie Industriepartnern wie Globalfoundries entstanden, der auch international Beachtung findet. Dort suchen Physiker, Ingenieure und Analyse-Experten nach neuen Wegen, um deutlich leistungsfähigere Elektronik durch räumliche Konstruktionsprinzipien zu erzeugen.

„Echte“ 3D-Chips bei Intel

Einer dieser Wege ist die „echte“ 3D-Konstruktion von Nanotransitoren, um diese dichter packen zu können und Leckstromprobleme zu lösen. Eine solche Bauweise hat 3D-Pionier Intel bereits stellenweise in der Produktion (Trigate-Transistor). Dieses „echte“ 3D ist vor allem interessant für Chipwerke, die modernste Chips in hohen Stückzahlen fertigen.

Die Trigate-Transistoren im „Ivy Bridge“-Prozessor von Intel sind dreidimensional aufgebaut. Abb.: Intel

Steigt auch Globalfoundries auf 3D um?

Der Übergang zu echten 3D-Transistoren dürfte daher auch beim Cluster-Partner Globalfoundries (GF) nur eine Frage der Zeit sein. Noch unklar ist aber, wann der weltweit zweitgrößte Chip-Auftragsfertiger auf 3D umsteigt und an welchen Konzernstandorten – sei es nun Dresden. New York oder vielleicht gar in einem neuen Chipwerk in der arabischen Wüste, das den GF-Anteilseignern eigentlich schon lange versprochen worden war…

Werbung

2,5D-Pfad soll zu kompakten Universalchips führen

Ein anderer Weg ist die sogenannte „2,5D“-Bauweise. Wie es der Name schon andeutet, ist dies eine Zwischenform aus zwei- und dreidimensionaler Chipintegration. Dabei werden Prozessoren, Speicher und andere Elektronikkomponenten auf kleinstem Raum dreidimensional vernetzt – indem man sie in einzelnen Funktionsschichten auf Siliziumscheiben (Wafer) gewissermaßen „übereinanderstapelt“ und dann vertikal durchkontaktiert, also elektrisch verbindet („TSV“-Technik). Dies könnte im Vergleich zur klassischen Mikroelektronik-Konstruktion „in der Ebene“ zu deutlich kompakteren Universalchips führen, wie sie beispielsweise im Automobilbau benötigt werden.

Prof. Ehrenfried Zschech. Foto: TUD

Diese Stapelidee klingt simpel, hat allerdings ihre Tücken: „Weil wir dabei unterschiedliche Materialien mit unterschiedlichen thermischen Ausdehnungskoeffizienten übereinander schichten, müssen wir dann auch dafür sorgen, dass diese Bausteine hinterher den thermischen Eigenspannungen im Betrieb stabil gewachsen sind“, nennt Prof. Zschech ein Beispiel für die Probleme, an denen die Dresdner Forscher arbeiten.

Millionenteurer Neubau für Nanoanalytik-Zentrum in Dresden

Zum sächsischen 3D-Elektronik-Cluster gehören zum Beispiel die Fraunhofer-Institute ASSID, IKTS und EAS in Dresden, aber auch das von Prof. Zschech geleitete DCN, das wiederum ein Teil des TU-Exzellenzzentrums für fortgeschrittene Elektronik (cfaed) ist. Dieses Nanoanalyse-Labor ist derzeit eher noch ein virtueller Verbund mit acht festen Mitarbeitern und modernster Mikroskoptechnik, mit denen zehn Forschungsgruppen kooperieren. Dies soll sich allerdings bald ändern: Im Zuge des millionenteuren cfaed-Neubaus auf dem Campus der TU Dresden erhält das DCN im Innenhof des Barkhausenbaus ein spezielles eigenes Gebäude, das weitgehend schwingungsfrei zur Außenwelt und den anderen Uni-Gebäuden abgeschottet ist.

Mit Spezialmikroskopen ähnlich diesem wollen die Dresdner Nanoanalytiker tief in die atomare Welt eindringen. Foto: Carl Zeiss

Bloß keinen Fahrstuhl!

Die Architekten waren daher sogar angehalten, den Laborneubau so zu entwerfen, dass keine Fahrstühle im Gebäude nötig sind – „denn auch die würden für Schwingungen sorgen, die wir bei unseren Analysen überhaupt nicht gebrauchen können“, sagte Zschech. 2017 soll der Neubau bezugsfertig sein. Autor: Heiko Weckbrodt

Ihre Unterstützung für Oiger.de!

Ohne hinreichende Finanzierung ist unabhängiger Journalismus nach professionellen Maßstäben nicht dauerhaft möglich. Bitte unterstützen Sie daher unsere Arbeit! Wenn Sie helfen wollen, Oiger.de aufrecht zu erhalten, senden Sie Ihren Beitrag mit dem Betreff „freiwilliges Honorar“ via Paypal an:

Vielen Dank!

Du muss angemeldet sein, um einen Kommentar zu veröffentlichen.